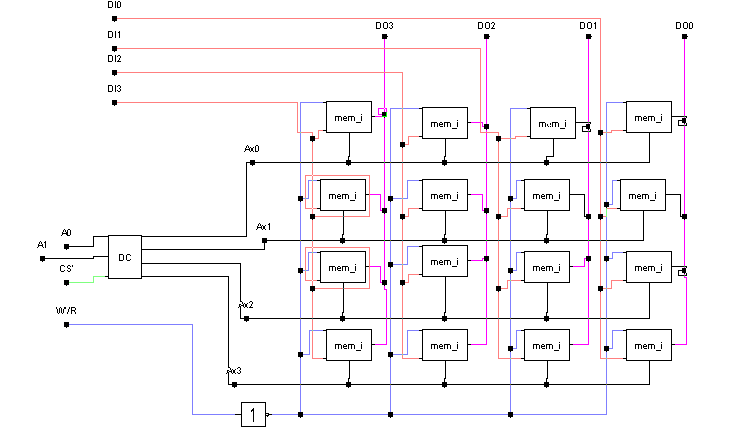

В качестве примера наРис. 5.3 показана микросхема ОЗУ К537РУ1. Она содержит 16 (24) бистабильных ячеек, организованных в виде матрицы из 4 строк (22) и 4-столбцов. Элементы каждого из столбцов соединены внутренней разрядной линией данных и хранят одноимённые биты всех слов.

Рис. 5.3. Микросхема ОЗУ 4х4 бит

Ячейка памяти состоит из 4х триггеров, управляемых общим сигналом. Слово п выбирается при подаче на линии адреса А0...А1 двоичного числа п.

При CS=0 одна из ячеек, соответствующая выставленному адресу, переходит в рабочее состояние, её сигналы поступают на входы элементов И(7…10).

При CS=1 на всех выходах дешифратора низкие уровни и, следовательно, все триггеры отключены от входных шин накопителя.

При CS=0 и W=0 на выбранную ячейку поступают информационные сигналы с входов DI0…DI3 и вырабатывается сигнал «Запись». Входная информация со входов DI0…DI3 записывается в ячейку.

При CS=0 и W=1 формируется сигнал «Чтение» и информация из выбранной ячейки читается с выходов DO0…DO3 .

В обоих случаях микросхема ОЗУ должна быть выбрана подачей лог.0 на вывод СS’. В зависимости от версии микросхемы интервал между подачей сигналов выборки и началом обращений к ней составляет от 100 до 150 нc. Если напряжение питания не пропадает, время хранения данных не ограничено. По этой причине микросхема К537РУ1 называется статическим ОЗУ (RАМ).

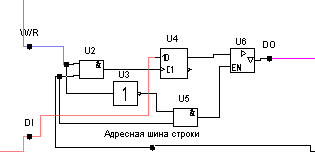

а) элемент статической памяти б) элемент динамической памяти

Рис. 5.4.Элементы памяти ОЗУ