В предыдущих разделах было показано, как можно любую логическую функцию представить в виде суммы произведений и реализовать с помощью схемы на основе вентилей И и ИЛИ и рассказывалось о реализации логической функции с применением мультиплексора. Теперь же речь пойдет об еще одном классе схем, обычно используемом для этой же цели. Описанные здесь схемы состоят из массивов логических элементов, которые для получения заданной суммы произведений можно программировать. Такие схемы называются ПЛУ — программируемыми логическими устройствами (Programmable Logic Device, PLD).

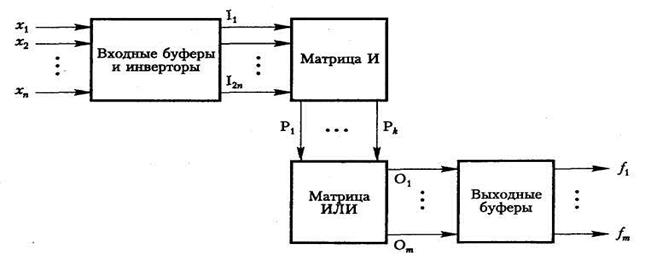

Блок-схема программируемого логического устройства показана на рис. 4.1. У него n входных переменных (х1..., хn) и m выходных функций (f1 ...,fm). Каждая функция fi реализуется как сумма произведений входных переменных. Значения переменных x1,..., хn в исходной форме и в форме дополнений подаются на входы матрицы И, где из них формируется k термов-произведений. Оттуда они передаются в матрицу ИЛИ, где формируются выходные функции. В этом разделе описываются два наиболее распространенных типа программируемых логических устройств.

Рис. 4.1. Блок-схема ПЛУ