2.1. Вводные замечания

2.1. Вводные замечания

Архитектура однокристального 8-разрядного n-МОП микропроцессора КР580ВМ80 (ВМ80) второго поколения [1, 61] аналогична архитектуре известного МП 8080 [23, 40, 56]. Схемотехнические и архитектурные особенности ВМ80 в сочетании с n-канальной технологией позволили уменьшить время выполнения команд типов регистр-регистр до 1,6 мкс, регистр-память до 2,8 мкс при тактовой частоте 2,5 МГц, что соответствует быстродействию 500 тыс. операций в секунду.

Для работы ВМ80 применяется три источника питания: –5 В (ток потребления менее 1 мА), +5 В (ток потребления менее 70 мА) и +12 В (ток потребления менее 50 мА). Кристалл МП, содержащий около 5000 транзисторов, помещен в корпус с двухрядным расположением 40 выводов и шагом 2,5 мм между ними. Синхронизация МП осуществляется от двухфазного внешнего генератора, амплитуда тактовых импульсов которого 12 В.

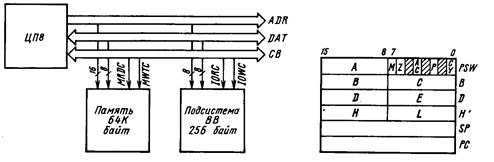

На рис. 2.1 приведена базовая структурная схема МС, построенной на базе МП ВМ80. В системе используется общая для хранения программ и данных основная память емкостью 64 К байт и подсистема ВВ емкостью 256 байт. Двунаправленная 8-разрядная шина данных DAT, 16-разрядная шина адреса ADR и шина управления СВ служат для организации побайтового обмена между отдельными модулями системы.

| Рис. 2.1. Схема микроЭВМ на базе микропроцессора ВМ80

| Рис. 2.2. Набор регистров микропроцнссора ВМ80

|