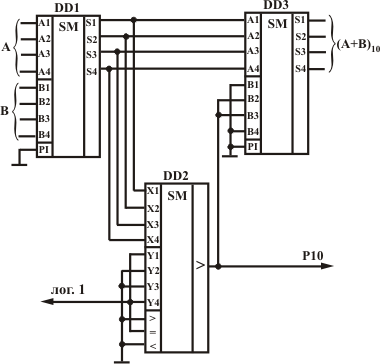

Чаще приходится суммировать десятичные числа. Ниже на рисунке приведена схема сумматора двоично-десятичных чисел на основе двоичных сумматоров.

Рис. 3 - Сумматор двоично-десятичных чисел

Операцию сложения выполняет сумматор DD1. При сумме большей или равной десяти на выходе микросхемы DD2, которая является схемой сравнения входов, формируется сигнал переноса Р10. На второй вход (Y1-Y4) микросхемы DD2 подается двоичный эквивалент числа 9 (1001). Сумматор DD3 осуществляет десятичную коррекцию результата суммирования. При отсутствии сигнала переноса на выходе микросхемы DD3 повторяется код числа, который был на выходе DD1, поскольку на входы В поданы лог. 0. При наличии сигнала переноса Р10=1 на входах В2-В3 устанавливаются лог. 1, что соответствует коду числа 6. Допустим есть числа А=8 и В=4. На выходе сумматора DD1 появляется код числа 12 (8+4=12). На выходе DD2 формируется сигнал переноса, сумматор DD3 выполняет операцию 12+6=18. Числу 18 соответствует код 10010. На выходах S сумматора DD3 устанавливается код 0010 (собственный перенос микросхемы DD3 не учитывается). Поскольку на выходе Р10 число 10, на выходах сумматора число 2 (0010), то в результате получается число 12.