В микросхемах n-МОП и р-МОП используются ключи на МОП-транзисторах с n-каналом и динамической нагрузкой и на МОП-транзисторах с p-каналом.

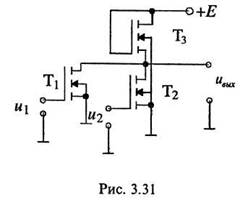

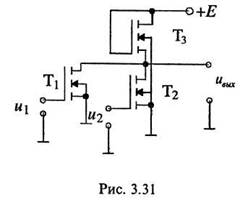

Рассмотрим базовый элемент логики п-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31). Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1и Т2. Если оба транзистора T1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения и1 и и2 имеют высокий уровень, то открывается один или оба транзистора Т1и Т2 и на входе устанавливается низкий уровень напряжения, т. е. реализуется функция

Рассмотрим базовый элемент логики п-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31). Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1и Т2. Если оба транзистора T1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения и1 и и2 имеют высокий уровень, то открывается один или оба транзистора Т1и Т2 и на входе устанавливается низкий уровень напряжения, т. е. реализуется функция

Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

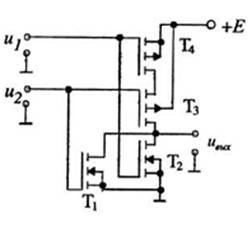

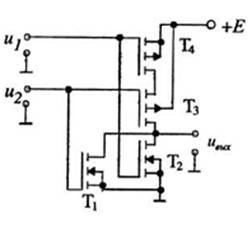

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32), Если входные напряжения имеют низкие уровни (и1 и и2 меньше порогового напряжения «-МОП-транзистора Uзипорогn), то транзисторы Т1и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения и1 и и2 имеют высокий уровень, превышающий Uзипорогn , то открывается один или оба транзистора Тх и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элемент реализует функцию

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32), Если входные напряжения имеют низкие уровни (и1 и и2 меньше порогового напряжения «-МОП-транзистора Uзипорогn), то транзисторы Т1и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения и1 и и2 имеют высокий уровень, превышающий Uзипорогn , то открывается один или оба транзистора Тх и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элемент реализует функцию  и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.

и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.

|

|

n-МОП |

КМОП |

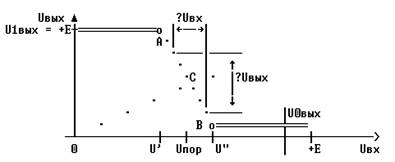

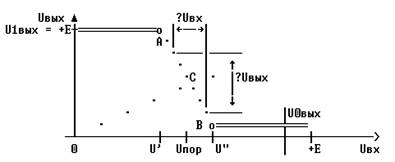

При нулевом входном напряжении (Uвх = 0) канал имеет очень большое сопротивление и на выход ключа подается напряжение питания через резистор R. Выходное напряжение логической единицы (U1вых) равно напряжению питания +Е. При увеличении входного напряжения выше U' сопротивление канала постепенно уменьшается и на выход подается часть напряженияисточника питания с делителя, образованного сопротивлением канала и резистором R (участок А-В на рис. слева). Сопротивление канала не может уменьшится до нуля. При входном напряжении выше U" сопротивление канала достигает минимальной величины и дальнейшее увеличение входного напряжения не влияет на сопротивление канала.

При входном напряжении выше U" выходное напряжение логического нуля (U0вых) определяется соотношением : U0вых = Е * Rк мин / (R + Rк мин). Где : Rк – минимальное сопротивление канала.

Величины U', U" и Rк мин - определяются технологическими параметрами: степень легирования канала, степень шероховатости поверхности канала, геометрические размеры канала; а также напряжением питания электронного ключа.

На участке А-В, т.е. при входном напряжении от U' до U" электронный ключ работает как аналоговый усилитель с коэффициентом усиления Ku =  Uвых /

Uвых /  Uвх .

Uвх .

Точка пересечения передаточной характеристики с биссектрисой первого квадранта (точка С на рис. слева) определяет пороговое напряжение Uпор электронного ключа.

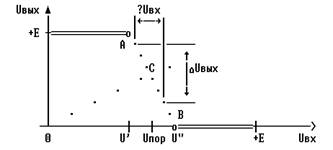

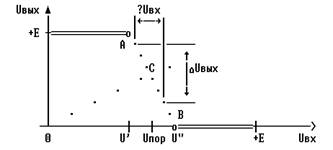

Переходная характеристика КМОП ключа приведена на рис. справа. При нулевом входном напряжении транзистор с n-каналом VT1 закрыт (сопротивление канала очень велико), а транзистор с р-каналом VT2 открыт (сопротивление канала – Rк мин ), т.к. к его затвору относительно истока приложено напряжение источника питания.

Поэтому на выходе ключа напряжение логической единицы : U1вых = +Е. При увеличении входного напряжения выше U' (точка А на рис. справа) начинает уменьшаться сопротивление канала транзистора VT1, а сопротивление канала VT2 - увеличивается. Выходное напряжение постепенно уменьшается и в конце участка А-В практически доходит до нуля (U0вых = 0) при полном закрывании транзистора VT2 и уменьшении сопротивления канала транзистора VT1 до величины Rк мин На участке А-В оба транзистора работают в активном режиме усиления аналогового сигнала с коэффициентом усиления по напряжению: Ku =  Uвых /

Uвых /  Uвх .

Uвх .

При этом оба канала имеют конечное сопротивление и через два транзистора течет сквозной ток от источника питания. С увеличением входного напряжения выше U" канал транзистора VT2 закрывается и ток через КМОП ключ от источника питания не потребляется. Таким образом, при входном напряжении ниже U' а также выше U" ток через КМОП ключ от источника питания практически не течет. Статическая потребляемая мошность близка к нулю. Пороговое напряжение Uпор определяется как точка пересечения передаточной характеристики с биссектрисой первого квадранта (точка С). Пороговое напряжение почти равно половине напряжения источника питания. Участок с напряжением U'- U" примерно равен 10..20% от напряжения источника питания, но имеет технологический разброс относительно середины напряжения источника питания. Поэтому входное напряжение низкого логического уровня U0вх должно быть менее 1/3 напряжения источника питания, а входное напряжение высокого логического уровня U1вх должно быть более 2/3 напряжения питания. Абсолютное значение напряжения источника питания +Е может изменяться в широких пределах от 3 до 15 Вольт. Это позволяет питать КМОП логические схемы от нестабилизированного источника питания, что значительно упрощает и удешевляет источник питания.

Характеристики рассмотренных элементов логики:

Диапазон напряжений питания, В |

3..15 |

Диапазон рабочих температур |

-40..+85 |

Входное напряжение (U1вх/ U0вх) |

>3,15/ < 0,9 |

Выходное напряжение (U1вых/ U0вых) |

Eп / 0,1 |

Входной ток, мкА (I1вх/I0вх) |

< 0,3/< 0,3 |

Выходной ток, мА (I1вых/I0вых) |

0,5/0,5 |

Максимальн.частота переключения, МГц |

до 150 МГц |

Рассмотрим базовый элемент логики п-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31). Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1и Т2. Если оба транзистора T1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения и1 и и2 имеют высокий уровень, то открывается один или оба транзистора Т1и Т2 и на входе устанавливается низкий уровень напряжения, т. е. реализуется функция

Рассмотрим базовый элемент логики п-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31). Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1и Т2. Если оба транзистора T1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения и1 и и2 имеют высокий уровень, то открывается один или оба транзистора Т1и Т2 и на входе устанавливается низкий уровень напряжения, т. е. реализуется функция  Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32), Если входные напряжения имеют низкие уровни (и1 и и2 меньше порогового напряжения «-МОП-транзистора Uзипорогn), то транзисторы Т1и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения и1 и и2 имеют высокий уровень, превышающий Uзипорогn , то открывается один или оба транзистора Тх и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элемент реализует функцию

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32), Если входные напряжения имеют низкие уровни (и1 и и2 меньше порогового напряжения «-МОП-транзистора Uзипорогn), то транзисторы Т1и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения и1 и и2 имеют высокий уровень, превышающий Uзипорогn , то открывается один или оба транзистора Тх и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элемент реализует функцию