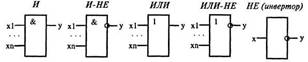

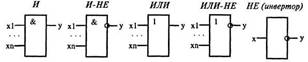

Логический элемент (вентиль) — это электронная схема, выполняющая некоторую простейшую логическую операцию. На рисунке приведены примеры условных графических обозначений некоторых логических элементов.

Логический элемент может быть реализован в виде отдельной интегральной схемы. Часто интегральная схема содержит несколько логических элементов.

Логические элементы используются в устройствах цифровой электроники для выполнения простого преобразования логических сигналов.

Наиболее широко используются следующие классы логических элементов: ТТЛ(транзисторно-транзисторная логика), ТТЛШ (транзисторно-транзисторная логика с диодами Шоттки), КМОП, ЭСЛ.

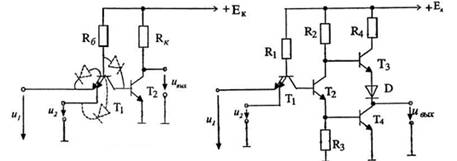

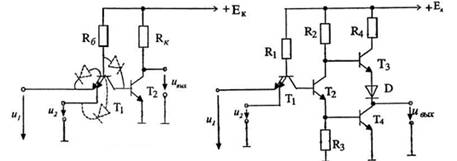

Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и сложный инвертор (рис. слева). Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).

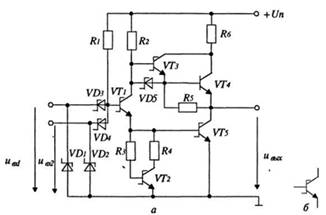

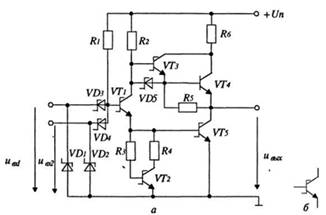

Базовый логический элемент ТТЛШ. В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29,а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29,6. Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. Транзистор VT4 — обычный биполярный транзистор. |

|

Если оба входных напряжения Uвх1 и Uвх2 имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Если оба входных напряжения Uвх1 и Uвх2 имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

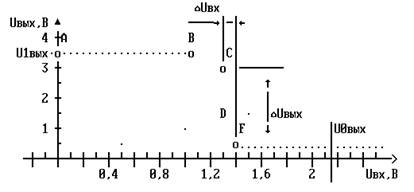

Амплітудно-передаточна характеристика.

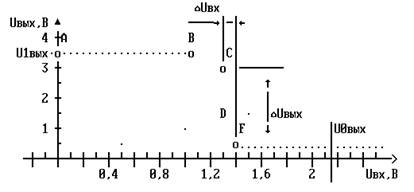

При нулевом напряжении на входе элемента ТТЛ выходное напряжение соответствует высокому логическому уровню U1вых (точка А).

Увеличение входного напряжения до величины 1,1 В соответствует закрытому состоянию сложного инвертора и практически не изменяет напряжение на выходе элемента. При напряжении на входе более 1,1 В (точка В) начинает открываться транзистор VT2, а транзисторVT4 остается закрытым, т.к. его переход база-эмиттер шунтируется резистором R3. Увеличение тока через транзистор VT2 вызывает увеличение падения напряжения на резисторах R2 и R3. Выходное напряжение эмиттерного повторителя VT3 (т.е. выходное напряжение ТТЛ элемента) уменьшается с ростом падения напряжения на R2 (участок В-С).

Увеличение падения напряжения на R3 до 0,5..0,6 В приводит к открыванию транзистора VT4 (см. точку С). Все транзисторы переходят в активный режим. Малые изменения входного напряжения ( Uвх) вызывают значительное уменьшение выходного напряжения (

Uвх) вызывают значительное уменьшение выходного напряжения ( Uвых). На участке C-F логический элемент работает как аналоговый усилитель с коэффициентом усиления по напряжению: Ku =

Uвых). На участке C-F логический элемент работает как аналоговый усилитель с коэффициентом усиления по напряжению: Ku =  Uвых /

Uвых /  Uвх.

Uвх.

Большинство реальных ТТЛ элементов имеют коэффициент усиления Ku в пределах от 5 до 20.

Правее точки F, когда увеличение входного напряжения приводит к насыщению транзисторов VT2 и VT4, дальнейшее изменение выходного напряжения происходить не может. Этот уровень выходного напряжения называется логическим нулем ТТЛ элементов и составляет : U0вых = 0,1...0,4 В. Точка D, лежащая на пересечении передаточной характеристики с биссектрисой первого квадранта (т.е. с прямой, на которой : Uвых = Uвх), определяет пороговый уровень напряжения Uпор (примерно 1,3..1,4 Вольта), разделяющий низкий и высокий логические уровни. Расстояния между низким логическим уровнем ТТЛ (U0 = 0,4 В) и пороговым напряжением (Uпор = 1,3 В), а также между высоким логическим уровнем ТТЛ (U1 > 3 В) и пороговым напряжением называются ЗАПАСОМ ПОМЕХОУСТОЙЧИВОСТИ. Этот запас определяет максимальное напряжение помехи на входе элемента, не изменяющее логическое состояние выхода.

Для ТТЛШ элементов характеристика имеет аналогичный характер за исключением того, что выходное напряжение логического нуля U0вых = 0,4..0,6 В, что является недостатком (следствие, уменьшенный на 0,2 Вольта запас помехоустойчивости).

Рассмотрим наиболее важные из параметров.

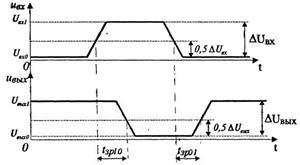

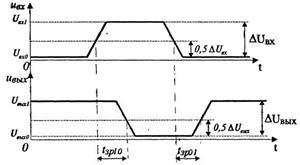

Быстродействие характеризуют временем задержки распространения сигнала tзр и максимальной рабочей частотой Fмакс. Обратимся к идеализированным временным диаграммам, соответствующим элементу НЕ (инвертору) (рис. 3.24). Через Uвх1 и Uвых1 обозначены уровни входного и выходного напряжений, соответствующие логической единице, а через Uвх0 и Uвых0 — соответствующие логическому нулю. Различают время задержки tзр10 распространения при переключении из состояния 1 в состояние 0 и при переключении из состояния 0 в состояние 1 — tзр01,а также среднее время задержки распространения tзр, причем

Быстродействие характеризуют временем задержки распространения сигнала tзр и максимальной рабочей частотой Fмакс. Обратимся к идеализированным временным диаграммам, соответствующим элементу НЕ (инвертору) (рис. 3.24). Через Uвх1 и Uвых1 обозначены уровни входного и выходного напряжений, соответствующие логической единице, а через Uвх0 и Uвых0 — соответствующие логическому нулю. Различают время задержки tзр10 распространения при переключении из состояния 1 в состояние 0 и при переключении из состояния 0 в состояние 1 — tзр01,а также среднее время задержки распространения tзр, причем  Время задержки принято определять по перепадам уровней 0,5DUвхи 0,5DUвых. Максимальная рабочая частота Fмакс — это частота, при которой сохраняется работоспособность схемы. Нагрузочная способность характеризуется коэффициентом объединения по входу Коб и коэффициентом разветвления по выходу Краз (иногда используют термин «коэффициент объединения по выходу»). Величина Коб — это число логических входов, величина Краз — максимальное число однотипных логических элементов, которые могут быть подключены к выходу данного логического элемента. Типичные значения их таковы: Коб = 2...8, Краз = 4...10. Для элементов с повышенной нагрузочной способностью Краз = 20...30.

Время задержки принято определять по перепадам уровней 0,5DUвхи 0,5DUвых. Максимальная рабочая частота Fмакс — это частота, при которой сохраняется работоспособность схемы. Нагрузочная способность характеризуется коэффициентом объединения по входу Коб и коэффициентом разветвления по выходу Краз (иногда используют термин «коэффициент объединения по выходу»). Величина Коб — это число логических входов, величина Краз — максимальное число однотипных логических элементов, которые могут быть подключены к выходу данного логического элемента. Типичные значения их таковы: Коб = 2...8, Краз = 4...10. Для элементов с повышенной нагрузочной способностью Краз = 20...30.

Помехоустойчивость в статическом режиме характеризуют напряжением Uист, которое называют статической помехоустойчивостью. Это такое максимально допустимое напряжение статической помехи на входе, при котором еще не происходит изменение выходных уровней логического элемента.

Важным параметром является мощность, потребляемая микросхемой от источника питания. Если эта мощность различна для двух логических состояний, то часто указывают среднюю потребляемую мощность для этих состояний.

Важными являются также следующие параметры:

напряжение питания;

входные пороговые напряжения высокого и низкого уровня Uвх 1порог и Uвх 0порог, соответствующие изменению состояния логического элемента;

выходные напряжения высокого и низкого уровней Uвых1 и Uвых0

Если оба входных напряжения Uвх1 и Uвх2 имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Если оба входных напряжения Uвх1 и Uвх2 имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона). Быстродействие характеризуют временем задержки распространения сигнала tзр и максимальной рабочей частотой Fмакс. Обратимся к идеализированным временным диаграммам, соответствующим элементу НЕ (инвертору) (рис. 3.24). Через Uвх1 и Uвых1 обозначены уровни входного и выходного напряжений, соответствующие логической единице, а через Uвх0 и Uвых0 — соответствующие логическому нулю. Различают время задержки tзр10 распространения при переключении из состояния 1 в состояние 0 и при переключении из состояния 0 в состояние 1 — tзр01,а также среднее время задержки распространения tзр, причем

Быстродействие характеризуют временем задержки распространения сигнала tзр и максимальной рабочей частотой Fмакс. Обратимся к идеализированным временным диаграммам, соответствующим элементу НЕ (инвертору) (рис. 3.24). Через Uвх1 и Uвых1 обозначены уровни входного и выходного напряжений, соответствующие логической единице, а через Uвх0 и Uвых0 — соответствующие логическому нулю. Различают время задержки tзр10 распространения при переключении из состояния 1 в состояние 0 и при переключении из состояния 0 в состояние 1 — tзр01,а также среднее время задержки распространения tзр, причем