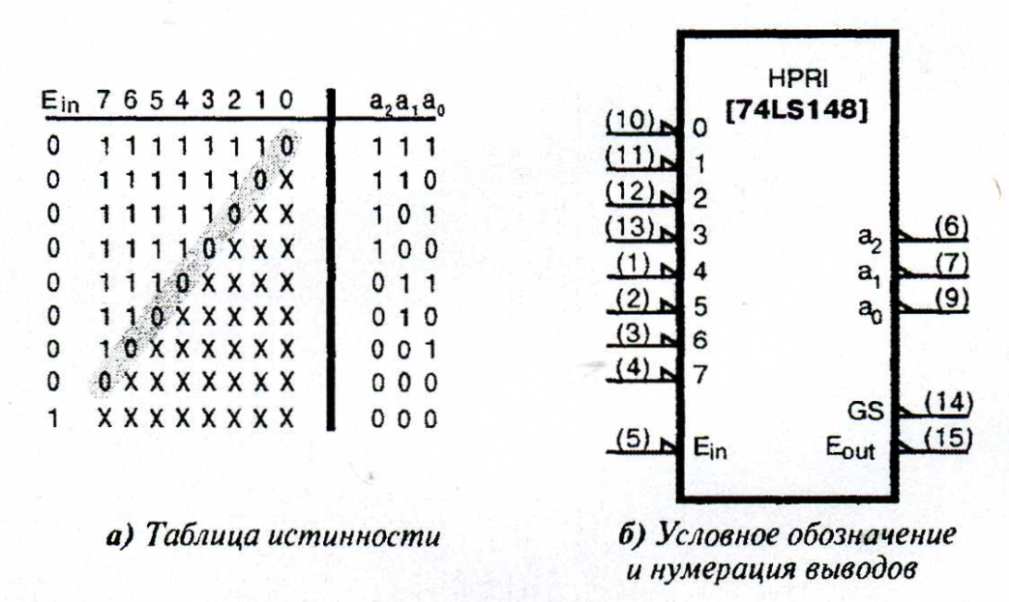

Приоритетный шифратор 74LS148 (К555ИВ1), показанный наРис. 3.2, выполняет обратное преобразование. Подача на один из входов НИЗКОГО уровня вызывает появление на выходе эквивалентного 3-битного значения. Так, если вход G = 0, то а2’a1’a0’ = 010 (101 в инверсной логике).

Рис. 3.2. Микросхема приоритетного шифратора

Если активный сигнал присутствует на нескольких входах, то выходное соответствует входу с наибольшим номером. Так, если НИЗКИЙ уровень присутствует на обоих входах 5’ и 3’, то выходное значение все равно будет составлять 010. Условное обозначении микросхемы приведено на Рис. 3.2. Работа микросхемы разрешается при НИЗКОМ уровне на входе Е1n. Выходы Еout, и GS’ используются при каскадном соединении микросхем для увеличения количества линий.