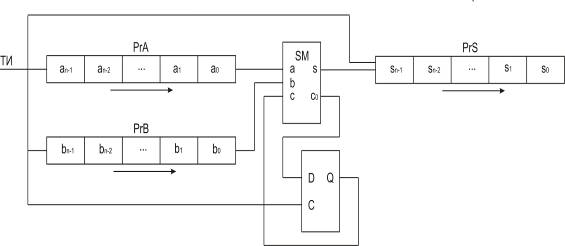

Сумматор для последовательных операндов содержит всего один одноразрядный сумматор, обрабатывающий числа последовательно разряд за разрядом, начиная с младшего. Сложив младшие разряды (a0 и b0), одноразрядный сумматор вырабатывает сумму (s0) для младшего разряда результата и перенос (c0), который запоминается на один такт.

В следующем такте складываются вновь поступившие разряды слагаемых (a1 и b1) с переносом из младшего разряда (с0) и т.д. Условная схема последовательного n‑разрядного сумматора (рис. 1), помимо одноразрядного двоичного сумматора, содержит сдвигающие регистры слагаемых и суммы, а также триггер, запоминающий перенос. Регистры и триггер тактируются сигналом ТИ.

Рис.1

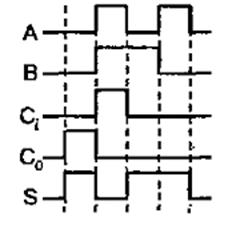

Рис.2

Рис. 1. Схема последовательного n‑разрядного сумматора.

Рис.2. временная дмаграмма соответствующая операции сложения двух операндов 101+110=1011 или в десятичном выражении 5+6=11.

Список литературы.

1.Угрюмов Е.П. Цифровая схемотехника.- СПб.: БХВ-Петербург, 2002 – 528 с.:ил.ISBN 5-8206-0100

2.http://ru.wikipedia.org/wiki/%D0%A1%D1%83%D0%BC%D0%BC%D0%B0%D1%82%D0%BE%D1%80