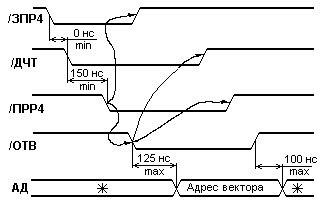

устройство, готовое прервать процессор, устанавливает сигнал /ЗПР4;

устройство, готовое прервать процессор, устанавливает сигнал /ЗПР4;

процессор в каждом рабочем цикле анализирует состояние линии /ЗПР4.

ближайшее по линии /ПРР4 устройство, имеющее наивысший приоритет из запросивших, при получении сигнала /ПРРП блокирует его дальнейшее распространение, сбрасывает сигнал /ЗПР4, устанавливает сигнал /ОТВ и адрес вектора прерывания на линиях АД;

– процессор читает адрес вектора прерывания с линий АД, сбрасывает сигналы /ДЧТ и /ПРР4 и приступает к обслуживанию прерывания;

– устройство, запросившее прерывание, снимает адрес вектора прерывания с линий АД и сбрасывает сигнал /ОТВ.

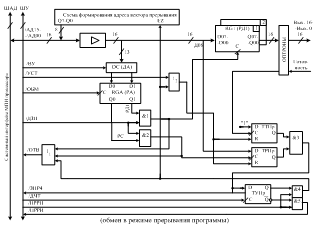

25. Пример схемы организации обмена в режиме прерывания в МПИ

25. Пример схемы организации обмена в режиме прерывания в МПИ

На рис. приведена схема модуля, иллюстрирующего организацию одноуровневого прерывания. Модуль предназначен для вывода информации на периферийное устройство по его готовности. В модуле имеется два адресуемых регистра: регистр данных (РД) и регистр состояния (РС). В состав регистра состояния входят триггер требования прерывания (ТТПр), триггер разрешения прерывания (ТРПр), триггер управления прерыванием (ТУПр). Триггер ТРПр предназначен для программного управления прерыванием. Если триггер ТРПр не установлен, то запрос прерывания от периферийного устройства через схему &3 не пройдёт. Прерывание от данного устройства запрещено.