|

|

ПаскальСиАссемблерJavaMatlabPhpHtmlJavaScriptCSSC#DelphiТурбо Пролог1С Компьютерные сетиСистемное программное обеспечениеИнформационные технологииПрограммирование Linux Unix Алгоритмические языки Аналоговые и гибридные вычислительные устройства Архитектура микроконтроллеров Введение в разработку распределенных информационных систем Введение в численные методы Дискретная математика Информационное обслуживание пользователей Информация и моделирование в управлении производством Компьютерная графика Математическое и компьютерное моделирование Моделирование Нейрокомпьютеры Проектирование программ диагностики компьютерных систем и сетей Проектирование системных программ Системы счисления Теория статистики Теория оптимизации Уроки AutoCAD 3D Уроки базы данных Access Уроки Orcad Цифровые автоматы Шпаргалки по компьютеру Шпаргалки по программированию Экспертные системы Элементы теории информации |

Схема мультиплексора и способы их наращивания. Схема демультиплексора и способы их наращивания.Дата добавления: 2014-11-27; просмотров: 2241; Нарушение авторских прав

|

Уроки php mysql Программирование Онлайн система счисления Калькулятор онлайн обычный Инженерный калькулятор онлайн Замена русских букв на английские для вебмастеров Замена русских букв на английские

Аппаратное и программное обеспечение

Графика и компьютерная сфера

Интегрированная геоинформационная система

Интернет

Компьютер

Комплектующие компьютера

Лекции

Методы и средства измерений неэлектрических величин

Обслуживание компьютерных и периферийных устройств

Операционные системы

Параллельное программирование

Проектирование электронных средств

Периферийные устройства

Полезные ресурсы для программистов

Программы для программистов

Статьи для программистов

Cтруктура и организация данных

| |||||||||

|

Не нашли то, что искали? Google вам в помощь! |

© life-prog.ru При использовании материалов прямая ссылка на сайт обязательна. |

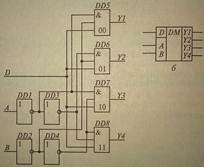

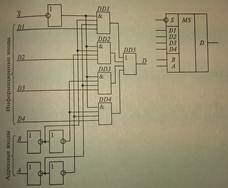

Мультиплексор (MS)- устройство, в котором в зависимости от управляющего кода осуществляется передача информации с одного из нескольких входов на выход. В схемах MS используются электронные ключи, замыкание которых производится под действием управляющих сигналов, приходящих, например, с дешифратора. Часто функции дешифратора и ключа объединены в одном элементе И. Схемы MS в интегральном исполнении имеют стробирующие входы S. При подаче на этот вход лог.0 дается разрешение на передачу информации на выход схемы в строго определенное время, определяемое длительностью строба (такт информации). Также использование этого хода позволяет строить схемы MS на большее число информационных входов. Сигналы проходят через логические элементы MS и реализуют один из минтермов. Если количество передаваемых входных сигналов превышает количество входов MS, применяют несколько схем, объединенных в мультиплексорное дерево.

Мультиплексор (MS)- устройство, в котором в зависимости от управляющего кода осуществляется передача информации с одного из нескольких входов на выход. В схемах MS используются электронные ключи, замыкание которых производится под действием управляющих сигналов, приходящих, например, с дешифратора. Часто функции дешифратора и ключа объединены в одном элементе И. Схемы MS в интегральном исполнении имеют стробирующие входы S. При подаче на этот вход лог.0 дается разрешение на передачу информации на выход схемы в строго определенное время, определяемое длительностью строба (такт информации). Также использование этого хода позволяет строить схемы MS на большее число информационных входов. Сигналы проходят через логические элементы MS и реализуют один из минтермов. Если количество передаваемых входных сигналов превышает количество входов MS, применяют несколько схем, объединенных в мультиплексорное дерево. Сумматор (SM)- узел АЛУ ЭВМ, выполняющий операцию суммирования кодов двух чисел. В зависимости от способа организации суммирования SM подразделяются на комбинационные (значение суммы на выходе исчезает со снятием слагаемых, поданных на вход) и накапливающие (результат суммирования сохраняется после снятия слагаемых со входа). По способу обработки многоразрядных чисел: параллельные (слагаемые всех разрядов вводятся одновременно), последовательные (осуществляют поразрядное сложение, начиная с младшего разряда, с запоминанием образовавшегося переноса до поступления более старших разрядов с последующим их суммированием).

Сумматор (SM)- узел АЛУ ЭВМ, выполняющий операцию суммирования кодов двух чисел. В зависимости от способа организации суммирования SM подразделяются на комбинационные (значение суммы на выходе исчезает со снятием слагаемых, поданных на вход) и накапливающие (результат суммирования сохраняется после снятия слагаемых со входа). По способу обработки многоразрядных чисел: параллельные (слагаемые всех разрядов вводятся одновременно), последовательные (осуществляют поразрядное сложение, начиная с младшего разряда, с запоминанием образовавшегося переноса до поступления более старших разрядов с последующим их суммированием).