ИС Компараторов кодов (Comparator) применяются для сравнения двух входных кодов А и В и выдаче на трех выходах результатов сравнения: А=В, А>В, А<В. На схемах компараторы кодов обозначаются двумя символами равенства «= =». Код типа ИС компаратора кодов в отечественных сериях – СП.

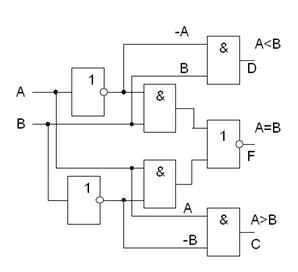

Логическая схема, выполняющая одноразрядного компаратора показана на рис 8.11.

Рис 8.11. Логическая структура одноразрядного компаратора

¾ Выход С=1 будет при А=1, В=0 (A>B).

¾ Выход D=1 будет при А=0, В=1 (A<B).

¾ Выход F=1 будет при А=В.

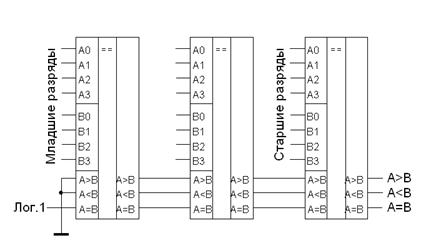

Два n-разрядных числа равны, когда попарно равны между собой все разряды этих чисел. Примером ИС компаратора кодов служит СП1- 4-х разрядный компаратор кодов в составе серии, показанный ниже.

а)

а)

|  б)

б)

|

Рис 8.12. 4-разрядный компаратор кодов СП1 (а) и каскадирование компараторов (б)

Если используется одиночная ИС, то для ее функционирования достаточно подать единицу на вход А=В: а состояния входов А>B и A<B не важны: на них надо обязательно подать либо нуль, либо единицу. Если ИС компараторов каскадируются (объединяются) для увеличения разрядности сравниваемых кодов, то выходные сигналы микросхемы, обрабатывающей младшие разряды кода нужно подать на одноименные входы микросхем, обрабатывающие старшие разряды кода.