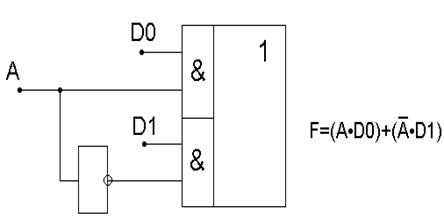

Рис. 1. Простейший MUX 2:1.

Рис. 2. Мультиплексор 4:1.

Рис. 2. Мультиплексор 4:1.

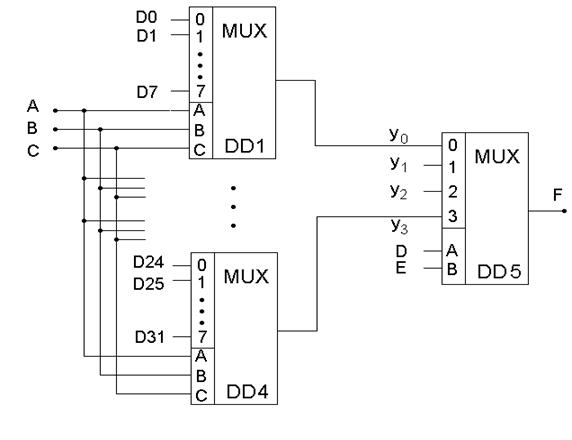

Рис.3. Пирамидальный MUX 32:1.

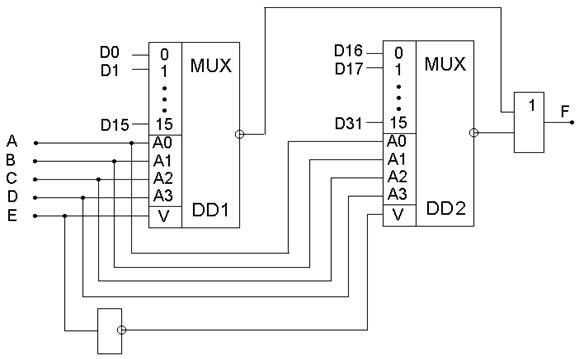

Рис. 4. Последовательное наращивание MUX.

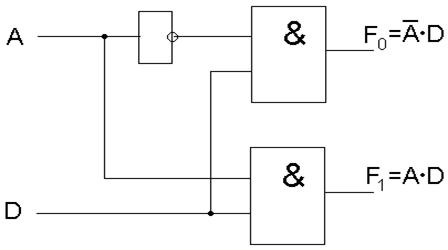

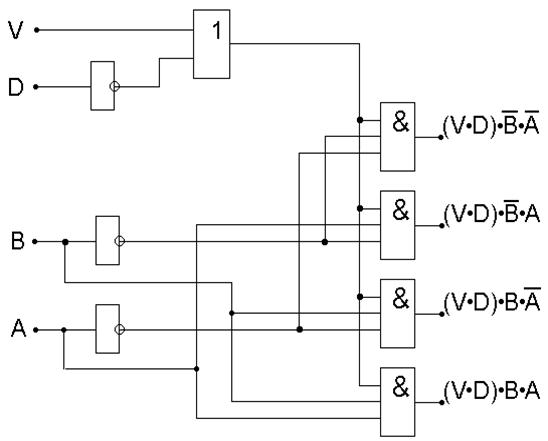

Рис. 5. Простейший демультиплексор 1:2.

Рис. 6. Демультиплексор 1:4.

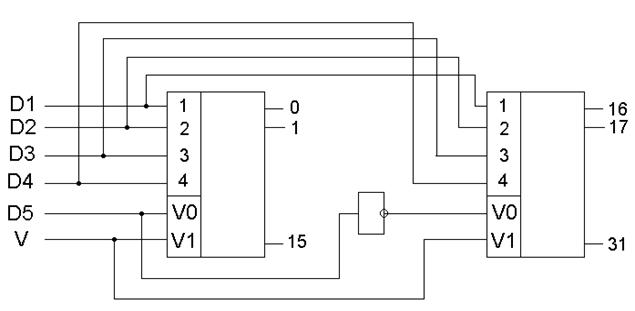

Рис. 7. Пирамидальная структура DMX 1:32.

Рис. 8. Последовательное наращивание DC 5:32.

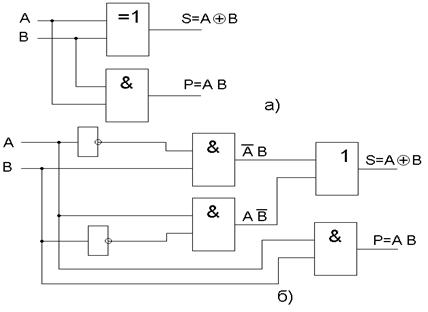

;

;  .

.

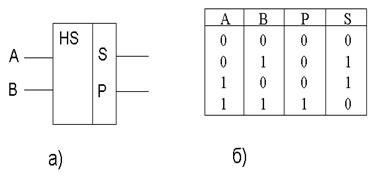

Рис. 9. Полусумматор: а – условное обозначение, б – таблица истинности.

Рис. 10. Логическая структура полусумматора в общем (а) и развернутом (б) виде.

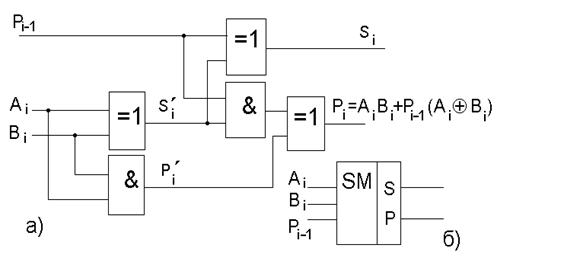

Рис. 11. Полный сумматор: а – логическая структура, б – условное обозначение.

Рис. 12. Логическая структура полного сумматора.

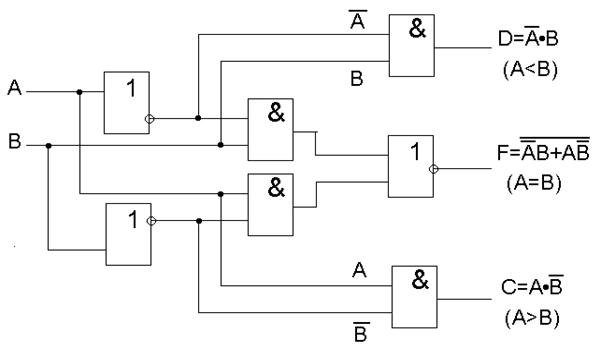

Рис. 13. Логическая структура одноразрядного компаратора.

Рис. 14. Четырехразрядный цифровой компаратор 564ИП2.

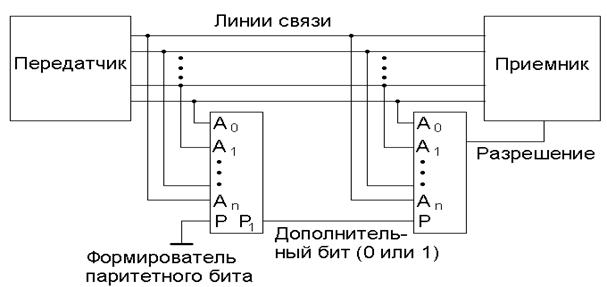

Рис. 15. Передача информации с контролем четности.

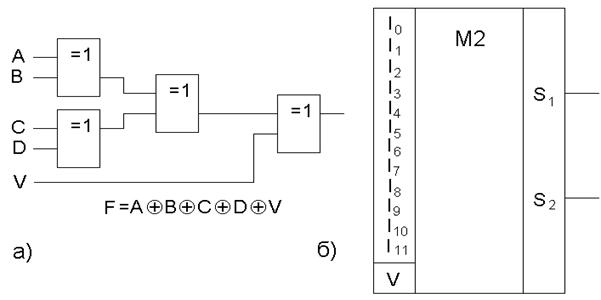

Рис. 16. Схема формирования паритетного бита из четырехразрядного слова (а), условное изображение микросхемы 564СА1.