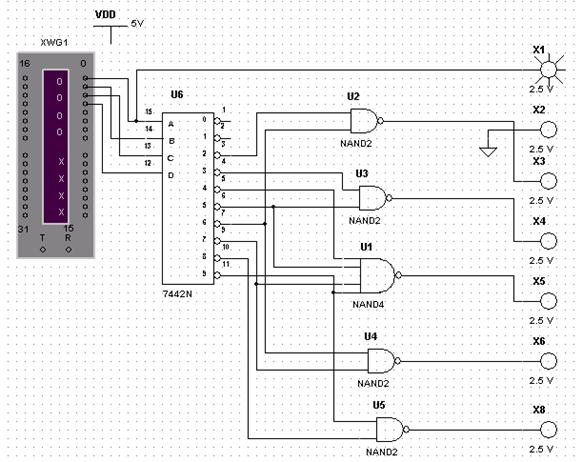

Задание: Провести исследование дешифратора двоичных сигналов на основе микросхемы серии ТТЛ – 7442N, составить схему наращивания.

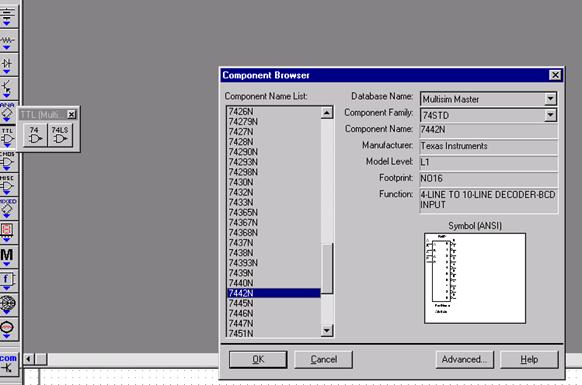

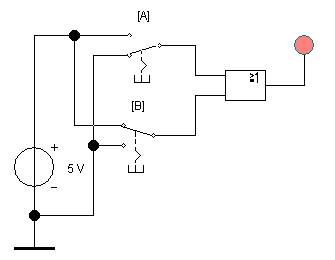

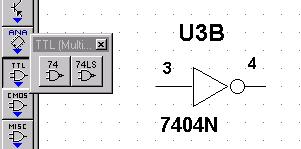

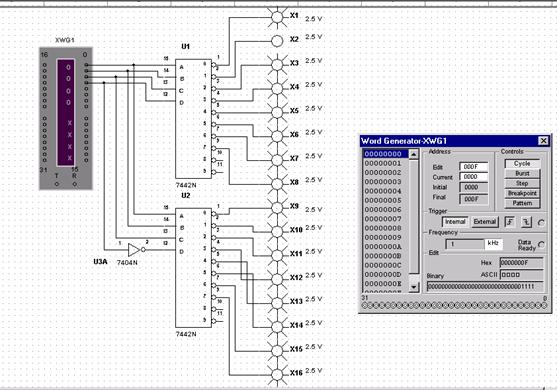

Из библиотеки элементов ТТЛ выберем дешифратор 7442N.

После нажатия мышью клавиши ОК, выбранный дешифратор переместится на рабочее поле.

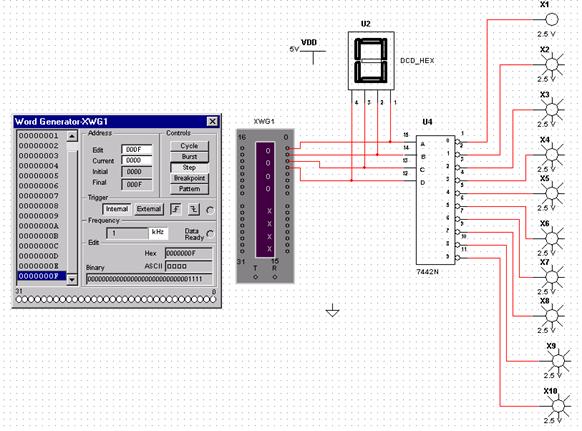

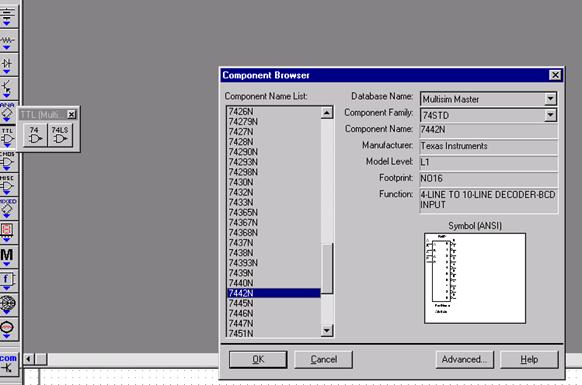

Оснастим схему средствами контроля и запрограммируем генератор слов.

Исследование схемы проведем в ручном режиме, поэтому при каждом нажатии курсором мыши на клавишу Step на панели генератора слов на входы дешифратора будут в пошаговом режиме поступать новые слова. Полученные данные занесем в табл.1.

Таблица 1

Состояния дешифратора 7442N

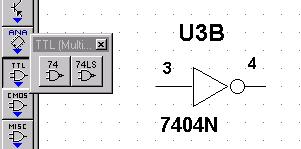

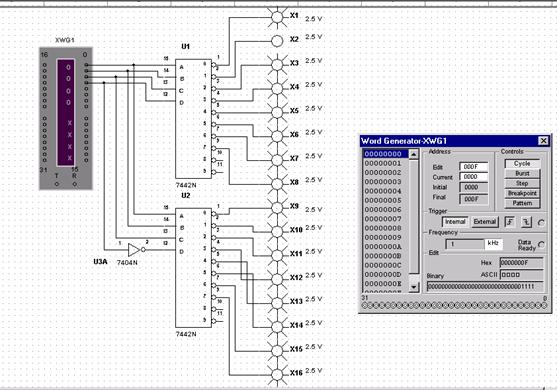

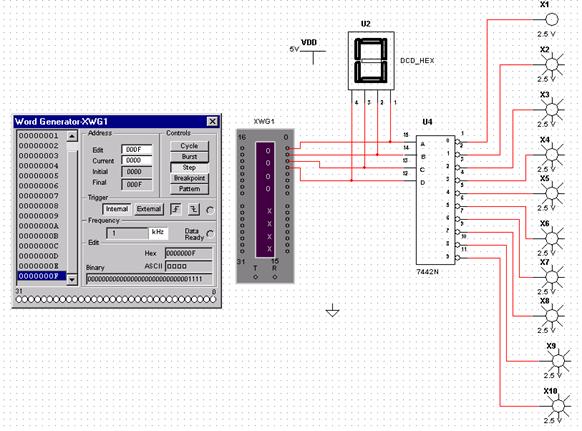

Вывод: Исследуемый дешифратор преобразует двоичный код поступающий на входы ABCD в сигнал низкого уровня, появляющийся на одном из десятичных выходов 0-9. Если десятичный эквивалент входного кода превышает 9, то на всех выходах 0-9 появляются напряжения высокого уровня. Если ограничить поступающий входной код от 0 до 8, то вход D можно использовать как разрешающий с низким активным уровнем, что дает возможность увеличить количество выходов до 16. Для инвертирования разряда D можно применить одну из секций микросхемы 7404N, которую также можно извлечь из библиотеки ТТЛ.

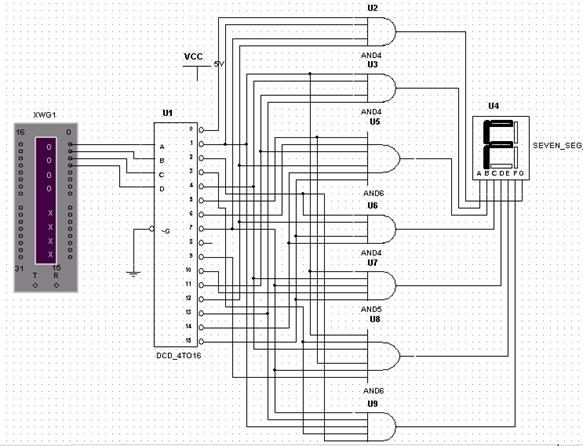

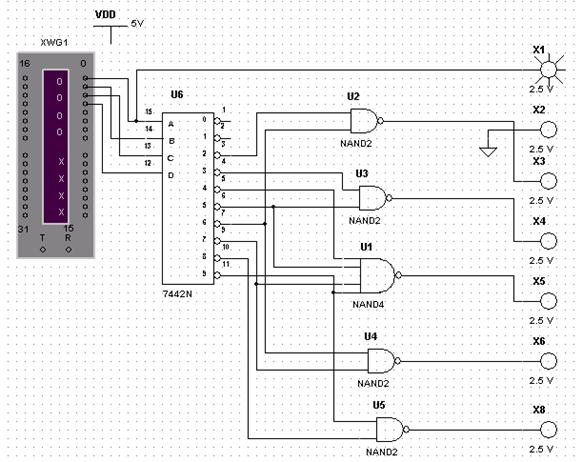

Соберем на рабочем поле схему наращивания, сигналы на входы подадим от генератора слов.

Результаты исследования занесем в табл. 2.

Таблица 2

Состояния дешифратора вида 4:16

| Вход

| Выход

|

| U2

| U1

| U1

| U2

|

| D

| C

| B

| A

| D

| C

| B

| A

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Варианты задания:

1.Спроектировать и исследовать схему преобразователя трехразрядного двоичного кода в сигналы управления одноразрядным 7-ми сегментным индикатором с выводами от каждого сегмента.

2Спроектировать и исследовать схему преобразователя четырехразрядного двоичного кода в сигналы управления одноразрядным 7-ми сегментным индикатором с выводами от каждого сегмента. Смотри приложение.

3.Спроектировать и исследовать схему преобразователя четырехразрядного двоичного кода в сигналы управления двумя разрядами 7-ми сегментных индикаторов с выводами от каждого сегмента.

4.Спроектировать и исследовать схему для дешифрации четырех разрядного двоичного кода на дешифраторах вида 3:8.

5.Спроектировать и исследовать схему преобразователя трехразрядного кода Грея в сигналы управления одноразрядным 7-ми сегментным индикатором с выводами от каждого сегмента.

6.Спроектировать и исследовать схему преобразователя четырехразрядного кода Грея в сигналы управления двумя разрядами 7-ми сегментных индикаторов с выводами от каждого сегмента.

7.Провести исследование приоритетного шифратора вида 8:3. Смотри приложение.

8.Провести исследование приоритетного шифратора вида 10:4.

9.Спроектировать и исследовать схему шифратора вида 16:4 с использованием двух шифраторов вида 8:3.

10.Спроектировать и исследовать мультиплексор вида 4:1, построенный на логических элементах И, ИЛИ, НЕ.

11.Спроектировать и исследовать схему мультиплексора вида 16:1 с использованием двух мультиплексоров вида 8:1.

12.Спроектировать и исследовать схему мультиплексора вида 16:1 из мультиплексоров вида 4:1.

13.Синтезировать и исследовать схему полусумматора двух одноразрядных двоичных чисел на логических элементах И-НЕ.

14.Синтезировать и исследовать схему полного одноразрядного сумматора на элементах 2И-ИЛИ-НЕ.

15.Спроектировать и исследовать схему четырехразрядного инкрементора на HALF ADDER (полусумматор) из библиотеки MISC.

16.Спроектировать и исследовать схему сумматора для сложения двух четырехразрядных двоичных чисел на HALF ADDER (полусумматор) из библиотеки MISC.

17.Спроектировать и исследовать схему сумматора-вычитателя двух четырехразрядных двоичных чисел.

18.Спроектировать и исследовать схему устройства для сравнения двух четырехразрядных двоичных чисел на основе четырехразрядного сумматора-вычитателя.

19.Спроектировать и исследовать схему устройства для вычисления среднего арифметического двух четырехразрядных двоичных чисел.

20.Спроектировать и исследовать схему для сложения четырехразрядного двоичного числа с пятиразрядной двоичной константой.

21.Спроектировать и исследовать схему для возведения в квадрат трехзначного двоичного числа. Смотри приложение.

22.Спроектировать и исследовать схему для перемножения двухразрядных двоичных чисел.

23.Спроектировать и исследовать схему для перемножения двухразрядного и трехразрядного двоичного числа.

24.Спроектировать и исследовать схему преобразователя кодов согласно нижеприведенной таблице.

Указание: схему выделения старшей единицы реализовать:

а) на шифраторе и дешифраторе вида 8:3;

в) на элементах М2. Смотри приложение;

с) на элементах И-НЕ.

| Входной код

| Показания индикатора по последней цифре номера зачетной книжки

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L

|

| П

|

| Н

|

| E

|

|

|

|

|

|

|

|

|

|

| А

|

|

| Г

|

|

| Р

|

|

|

|

|

|

|

|

|

|

|

|

| b

|

| F

|

|

|

| О

|

| L

| A

|

|

|

|

|

|

|

|

|

| C

|

|

| С

|

|

| П

|

|

| C

|

|

|

|

|

|

|

|

|

| d

|

| d

|

| С

|

| Ь

|

| A

| L

|

|

|

|

|

|

|

|

|

| E

|

|

| S

| А

|

| Г

|

|

|

|

|

|

|

|

|

|

|

|

| F

|

| P

|

|

|

| Е

|

| H

|

|

|

|

|

|

|

|

|

|

| H

|

|

| E

| P

|

| Ч

|

|

|

|

|

|

|

|

|

|

|

|

| P

|

| C

|

|

|

| Ц

|

| d

| F

|

25. Спроектировать и исследовать схему преобразователя трехразрядных двоичных кодов на мультиплексорах вида 8:1, согласно нижеприведенной таблице.

ПРИЛОЖЕНИЕ

В приложении приводятся схемы реализации некоторых вариантов заданий. Следует помнить, что приведенные схемы не претендуют на роль «истины в последней инстанции», а только демонстрируют возможности программы Multisim. Например, исследование шифратора вида 8:3 можно проводить в режиме ручного управления при помощи кнопок (схема 2), а можно автоматизировать этот процесс при помощи программируемого генератора слов, как это сделано в схеме 3.

С Х Е М Ы

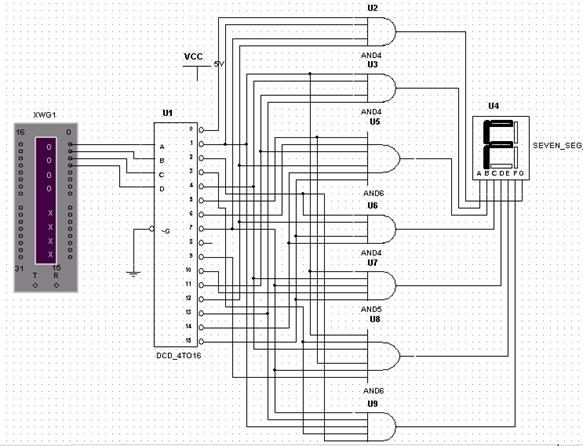

Схема 1. Дешифратор управления сегментами индикатора

В схеме применен некий гипотетический дешифратор имеющий инверсные выходы из библиотеки MISC.Если принцип образования схемы понятен, попытайтесь самостоятельно сконструировать аналогичный преобразователь с использованием дешифратора с прямыми выходами, например 4028 из библиотеки СMOS (КМОП).

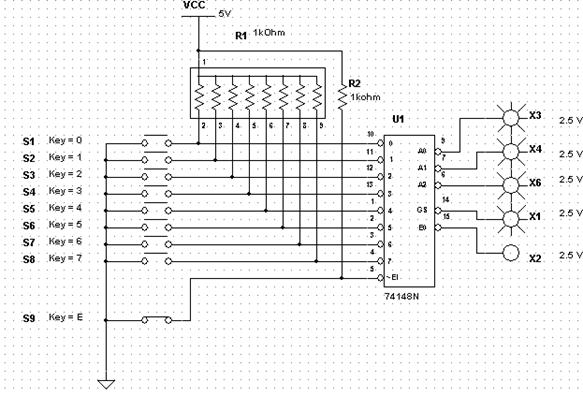

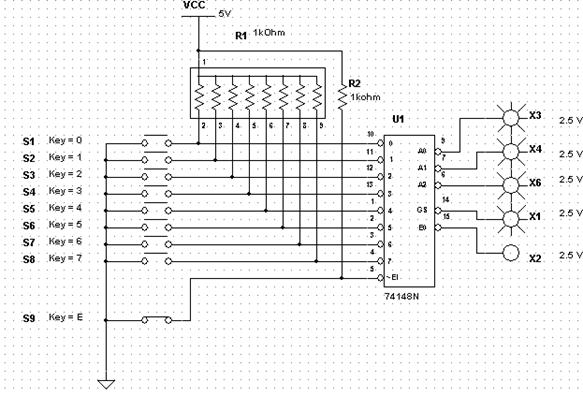

Схема 2. Исследование шифратора 74148 вида 8:3 в ручном режиме.

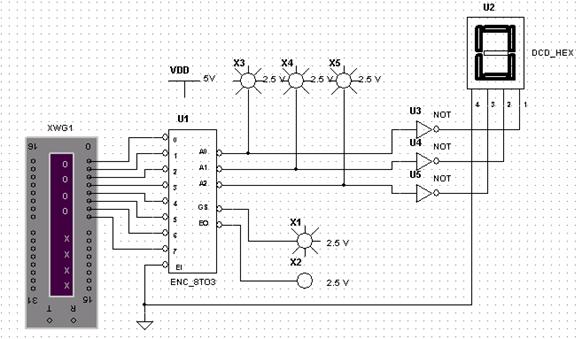

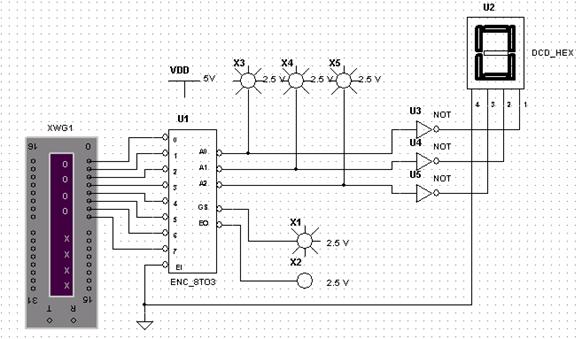

Схема 3. Исследование шифратора вида 8:3 при помощи генератора слов.

Схема 4. Устройство для возведения в квадрат двоичных чисел.

Схема 5. Преобразователь унитарного кода в семисегментный с узлом выделения старшей единицы на элементах М2.

Послідовність виконання роботи

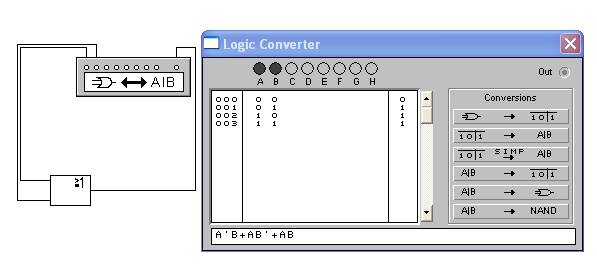

1. Ознайомитись з основними логічними елементами АБО, І і НЕ та роботою логічного перетворювача програми схемотехнічного моделювання Electronics Workbench.

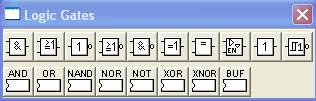

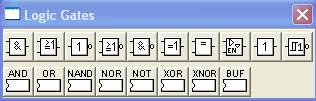

Поле логічних елементів відкривається клацанням “мишки” на зображенні  (Logic Gates), рис. 1.

(Logic Gates), рис. 1.

Рис. 1

На робоче поле логічні елементи переміщують пересуванням „мишки”, натиснувши ліву кнопку на їх зображенні.

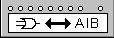

Для дослідження логічних елементів використовується логічний перетворювач (Logic Converter), який знаходиться в полі контрольно-вимірювальних приладів  (Instruments), рис. 2.

(Instruments), рис. 2.

Рис. 2

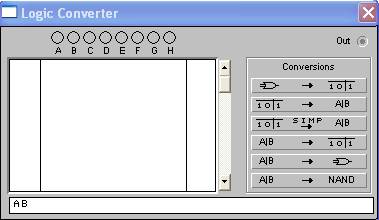

Зображення логічного перетворювача (Logic Converter)  переміщують на робоче поле пересуванням „мишки”, натиснувши ліву кнопку на його зображенні. На робочому полі виникає схемне зображення приладу, рис. 3, до якого приєднують логічні схеми, які необхідно дослідити.

переміщують на робоче поле пересуванням „мишки”, натиснувши ліву кнопку на його зображенні. На робочому полі виникає схемне зображення приладу, рис. 3, до якого приєднують логічні схеми, які необхідно дослідити.

Рис. 3

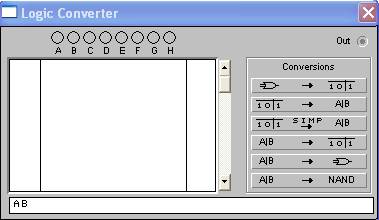

Подвійним клацанням лівою кнопкою мишки по цьому зображенню відкривається зображення передньої панелі логічного перетворювача, рис. 4.

Рис. 4

На зображенні передньої панелі перетворювача знаходяться вісім входів (позначених літерами від А до Н) та один вихід (Out). Вони не активні в схемному відношенні, але відповідають затискачам схемного зображення приладу.

Кільця над літерами входів є кнопки, натисканням на які, задаються комбінації вхідних аргументів до таблиці істинності. Значення вихідних логічних величин установлюють відповідно до таблиці істинності.

В правій частині панелі знаходяться клавіші режимів роботи логічного перетворювача (Conversions):

- отримання функції алгебри логіки (ФАЛ) логічного пристрою в вигляді таблиці істинності;

- отримання функції алгебри логіки (ФАЛ) логічного пристрою в вигляді таблиці істинності;

- перетворення ФАЛ логічного пристрою в вигляді таблиці істинності в алгебраїчний вираз;

- перетворення ФАЛ логічного пристрою в вигляді таблиці істинності в алгебраїчний вираз;

- спрощення алгебраїчного виразу ФАЛ;

- спрощення алгебраїчного виразу ФАЛ;

- перетворення ФАЛ в вигляді алгебраїчного виразу в ФАЛ в вигляді таблиці істинності;

- перетворення ФАЛ в вигляді алгебраїчного виразу в ФАЛ в вигляді таблиці істинності;

-побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі основних логічних операцій АБО, І і НЕ;

-побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі основних логічних операцій АБО, І і НЕ;

- побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі І-НЕ.

- побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі І-НЕ.

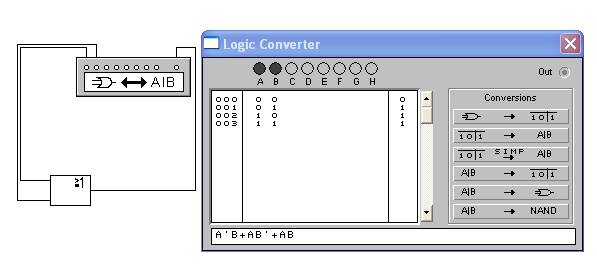

2. Виконати відповідно до режимів роботи логічного перетворювача дослідження основних логічних операцій АБО, І та НЕ. Схема дослідження логічної операції АБО наведена, як приклад, на рис. 5.

Рис. 5

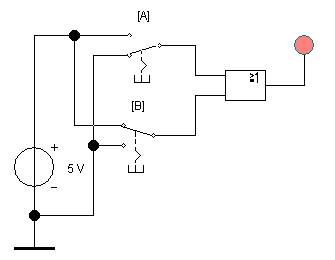

3. Побудувати схеми експериментального дослідження роботи основних логічних елементів АБО, І та НЕ. Комбінації вхідних аргументів задавати ключами (поле компонент  (Basic)) та джерелом напруги Е = 5 В (поле компонент

(Basic)) та джерелом напруги Е = 5 В (поле компонент  (Sources)). Виходи логічних елементів доповнити індикатором (поле компонент

(Sources)). Виходи логічних елементів доповнити індикатором (поле компонент  (Indicators)). На рис. 6, як приклад, наведено схему дослідження роботи логічного елемента АБО.

(Indicators)). На рис. 6, як приклад, наведено схему дослідження роботи логічного елемента АБО.

4. Провести дослідження логічних елементів. Для цього комбінуючи станом ключів і натискаючи кнопку  (запуск моделювання), що розміщена в правому куті екрану, скласти таблиці істинності логічних елементів та переконатись в правильності їх функціонування.

(запуск моделювання), що розміщена в правому куті екрану, скласти таблиці істинності логічних елементів та переконатись в правильності їх функціонування.

Рис. 6

АБО I НЕ

№ 2. Дешифратори

Мета роботи: навчитись складати таблиці істинності, записувати відповідно до них логічні функції, будувати та досліджувати функціональні схеми дешифраторів.

(Logic Gates), рис. 1.

(Logic Gates), рис. 1.

(Instruments), рис. 2.

(Instruments), рис. 2.

переміщують на робоче поле пересуванням „мишки”, натиснувши ліву кнопку на його зображенні. На робочому полі виникає схемне зображення приладу, рис. 3, до якого приєднують логічні схеми, які необхідно дослідити.

переміщують на робоче поле пересуванням „мишки”, натиснувши ліву кнопку на його зображенні. На робочому полі виникає схемне зображення приладу, рис. 3, до якого приєднують логічні схеми, які необхідно дослідити.

- отримання функції алгебри логіки (ФАЛ) логічного пристрою в вигляді таблиці істинності;

- отримання функції алгебри логіки (ФАЛ) логічного пристрою в вигляді таблиці істинності; - перетворення ФАЛ логічного пристрою в вигляді таблиці істинності в алгебраїчний вираз;

- перетворення ФАЛ логічного пристрою в вигляді таблиці істинності в алгебраїчний вираз; - спрощення алгебраїчного виразу ФАЛ;

- спрощення алгебраїчного виразу ФАЛ; - перетворення ФАЛ в вигляді алгебраїчного виразу в ФАЛ в вигляді таблиці істинності;

- перетворення ФАЛ в вигляді алгебраїчного виразу в ФАЛ в вигляді таблиці істинності; -побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі основних логічних операцій АБО, І і НЕ;

-побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі основних логічних операцій АБО, І і НЕ; - побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі І-НЕ.

- побудова схеми логічного пристрою за ФАЛ в вигляді алгебраїчного виразу в базисі І-НЕ.

(Basic)) та джерелом напруги Е = 5 В (поле компонент

(Basic)) та джерелом напруги Е = 5 В (поле компонент  (Sources)). Виходи логічних елементів доповнити індикатором (поле компонент

(Sources)). Виходи логічних елементів доповнити індикатором (поле компонент  (Indicators)). На рис. 6, як приклад, наведено схему дослідження роботи логічного елемента АБО.

(Indicators)). На рис. 6, як приклад, наведено схему дослідження роботи логічного елемента АБО.

(запуск моделювання), що розміщена в правому куті екрану, скласти таблиці істинності логічних елементів та переконатись в правильності їх функціонування.

(запуск моделювання), що розміщена в правому куті екрану, скласти таблиці істинності логічних елементів та переконатись в правильності їх функціонування.