Цифровий стандарт керування супутниковим обладнанням – DiSEqC (Digital Satellite Equipment Control) – розроблений компанією Eutelsat з метою спрощення контролю периферійних пристроїв.

З розвитком супутникового телебачення все більш актиульною ставала задача керування конверторами (перемикання піддіапазонів у смузі 10,70 – 12,75 ГГц, вибір типу поляризації, організація сумісної роботи конвертора С-діапазону з універсальним конвертором Ku-діапазону) та електроприводом антени. Існуючий в даний час набір сигналів керування конвертором – 13/18 В та тоновий сигнал 22 кГц – подається на антену по коаксиальному кабелю, а сигнал керування електроприладом – по окремому силовому.

Стандарт DiSEqC має наступні переваги:

- є можливість керування універсальними конверторами, які знаходяться у складі мультифокусної антени;

- для всіх видів перемикання конвертору та керування електроприводом використовується один кабель;

- застосовуються стандартні команди керування;

- ліквідовуються проблеми перемикання, обумовлені несумісністю різних компонентів системи;

- забезпечується сумісність з існуючими сигналами керування;

- має підвищену надійність.

Робота системи DiSEqC основана на перемиканні тонового сигналу 22 кГц. Значенням “0” та “1” відповідає визначена продовженність імпульсу (мал. 5.20). Всі повідомлення складаються з байтів даних, кожний з яких супроводжується одним бітом перевірки на парність. Будь-яка команда включає в себе адресний, стартовий та інформаційний байти.

Для керування електроприводом розроблені спеіальний протокол. У відповідності з ним після адресної інформації, визначаючої необхідний пристрій, передається кратне необхідній кількості обертів електродвигуна число імпульсів.

В даний час найбільше розповсюдження отримали системи mini- DiSEqC, які забезпечують виконання обмеженого набору команд. Зрозуміло, що з розвитком стандарту (вже зараз існують версії 1.0, 2.0, 3.0) з його допомогою стане можливим повне керування всіим спектром обладнання.

Триггер RS-типа. Принцип работы. Временные диаграммы. Функциональная схема. Параметры. Примеры использования.

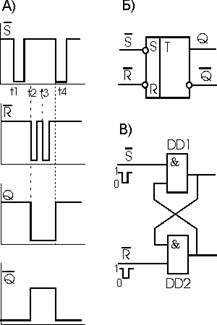

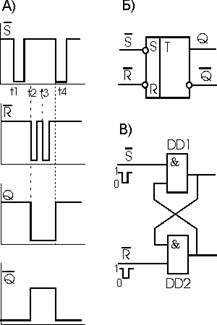

Триггеры представляют собой импульсные устройства, которые характеризуются наличием двух устойчивых состояний. Простейший триггер имеет два входа и два выхода (рис. 4.1). Выходы обозначают Q и /Q. Выход Q называют прямым, a /Q - инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q = 1, то /Q = 0, либо если Q = 0, то /Q = 1. Необходимо еще отметить, что состояние триггера, при котором Q = 1, a /Q = 0, называют единичным. При нулевом состоянии триггера Q = 0 и /Q = 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется. В зависимости от функциональной связи между логическими сигналами на входах и выходах триггеры в интегральном исполнении имеют следующие наименования: /R/S, RS, D, Т, JK и некоторые другие. Теми же буквами обозначают и входы триггеров.

Триггеры представляют собой импульсные устройства, которые характеризуются наличием двух устойчивых состояний. Простейший триггер имеет два входа и два выхода (рис. 4.1). Выходы обозначают Q и /Q. Выход Q называют прямым, a /Q - инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q = 1, то /Q = 0, либо если Q = 0, то /Q = 1. Необходимо еще отметить, что состояние триггера, при котором Q = 1, a /Q = 0, называют единичным. При нулевом состоянии триггера Q = 0 и /Q = 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется. В зависимости от функциональной связи между логическими сигналами на входах и выходах триггеры в интегральном исполнении имеют следующие наименования: /R/S, RS, D, Т, JK и некоторые другие. Теми же буквами обозначают и входы триггеров.

На рис. 4.1 показан простейший триггер - типа /R/S. Здесь использованы только два ЛЭ И-НЕ. Назначение входов: /S-для установки триггера в единичное состояние и /R - для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рис. 4.1, а). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q = 1 и /Q = 0, т. е. триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение высокого, а на выходе - низкого (/Q = 0) уровня. В то же время на одном из входов DD1 напряжение низкого, а на выходе - высокого уровня. Если теперь на вход /S поступает сигнал с обозначенной полярностью (момент t1, рис. 4.1, а), состояние триггера не изменится, потому что поступление сигнала на второй вход DD1 временно изменит только сочетание сигналов на входах (до подачи сигнала оно было 1 и 0, а стало 0 и 0), но выходное состояние DD1 остается при этом неизменным. Если, однако, сигнал поступит на вход /R (момент t2), на обоих входах DD2 уже окажутся напряжения разного уровня, состояние ЛЭ изменится и на выходе его будет напряжение высокого уровня. На обоих входах DD1 окажутся напряжения высокого уровня, а на выходе – низкого, т. е. триггер "опрокинется" и перейдет в другое состояние: Q =О и /Q = 1.

На рис. 4.1 показан простейший триггер - типа /R/S. Здесь использованы только два ЛЭ И-НЕ. Назначение входов: /S-для установки триггера в единичное состояние и /R - для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рис. 4.1, а). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q = 1 и /Q = 0, т. е. триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение высокого, а на выходе - низкого (/Q = 0) уровня. В то же время на одном из входов DD1 напряжение низкого, а на выходе - высокого уровня. Если теперь на вход /S поступает сигнал с обозначенной полярностью (момент t1, рис. 4.1, а), состояние триггера не изменится, потому что поступление сигнала на второй вход DD1 временно изменит только сочетание сигналов на входах (до подачи сигнала оно было 1 и 0, а стало 0 и 0), но выходное состояние DD1 остается при этом неизменным. Если, однако, сигнал поступит на вход /R (момент t2), на обоих входах DD2 уже окажутся напряжения разного уровня, состояние ЛЭ изменится и на выходе его будет напряжение высокого уровня. На обоих входах DD1 окажутся напряжения высокого уровня, а на выходе – низкого, т. е. триггер "опрокинется" и перейдет в другое состояние: Q =О и /Q = 1.

Из сказанного следует, что смена состояния триггера происходит только при чередовании сигналов низкого уровня на входах /S и /R. При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q = 0 или Q = 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается.

Из сказанного следует, что смена состояния триггера происходит только при чередовании сигналов низкого уровня на входах /S и /R. При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q = 0 или Q = 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается.

| /Rn

| /Sn

| Qn+1

| /Qn+1

|

|

|

| Qn

| /Qn

|

|

|

|

|

|

|

|

|

|

|

|

|

| неопределенное состояние

|

|

Работа /R/S-триггера характеризуется таблицей состояний (индексы n и n+1 означают принадлежность сигнала моменту времени tn и следующему за ним tn+1):

Не разрешается одновременная подача напряжения низкого уровня на оба входа /R/S-триггера.

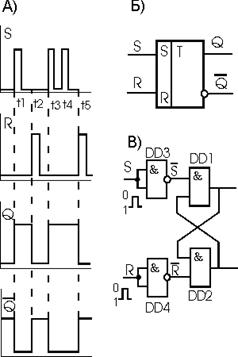

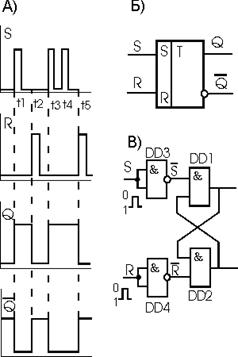

Триггер типа RS, как и /R/S-триггер, "запоминает", на какой из двух входов (R или S) поступил последний сигнал: если на вход R, триггер находится в нулевом состоянии (Q = 0 и /Q = 1), а если на вход S, то в единичном состоянии (Q = 1 и /Q = 0).

На рис. 4.2 показана схема RS-триггера, выполненного на ЛЭ И-НЕ. Она отличается от схемы /R/S-триггера тем, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только обеспечивают необходимый уровень входных сигналов.

Изменение входных сигналов от низкого уровня до высокого приводит к смене состояния триггера (моменты t1, t2, t2 и t5; в момент t4 опрокидывания не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент - t3).

Изменение входных сигналов от низкого уровня до высокого приводит к смене состояния триггера (моменты t1, t2, t2 и t5; в момент t4 опрокидывания не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент - t3).

| Rn

| Sn

| Qn+1

| /Qn+1

|

|

|

| Qn

| /Qn

|

|

|

|

|

|

|

|

|

|

|

|

|

| неопределенное состояние

|

|

Все сказанное относительно RS-триггера сохраняет силу и для /R/S-триггера. Единственное различие касается инверсии уровней входных сигналов (R вместо /R и S вместо /S).

Работа RS-триггера характеризуется следующей таблицей состояний:

Триггер D-типа. Принцип работы. Временная диаграмма. Функциональная схема. Параметры. Примеры использования.

Триггер типа D – это устройство с двумя устойчивыми выходными состояниями. Сменой состояния управляют сигналы на информационном входе D (рис. 5.1), но переключение происходит не сразу, а с приходом тактового импульса на второй вход С. Важнейшее свойство D-триггеров в том, что, как только на вход С поступает импульс, на выходе Q устанавливается тот же уровень напряжения, который в этот момент действует на входе D, т. е. переброс триггера происходит с некоторым отставанием dt относительно смены сигнала на входе D. Поэтому D-триггеры еще называют триггерами задержки.

Триггер типа D – это устройство с двумя устойчивыми выходными состояниями. Сменой состояния управляют сигналы на информационном входе D (рис. 5.1), но переключение происходит не сразу, а с приходом тактового импульса на второй вход С. Важнейшее свойство D-триггеров в том, что, как только на вход С поступает импульс, на выходе Q устанавливается тот же уровень напряжения, который в этот момент действует на входе D, т. е. переброс триггера происходит с некоторым отставанием dt относительно смены сигнала на входе D. Поэтому D-триггеры еще называют триггерами задержки.

Триггер, схема которого показана на рис. 5.1, в, содержит четыре ЛЭ И-НЕ. Здесь DD1 и DD2 образуют знакомый /R/S-триггер. Дополнительные элементы DD3 и DD4 превращают его в D-триггер. Действует D-триггер следующим образом. Если D = 1, то при наличии тактового импульса на выходе DD3 формируется сигнал, вид которого показан на рис. 5.1,в. Сигнал действует на /R/S-триггер подобно сигналу /S, и на выходе Q устанавливается напряжение высокого уровня (Q = 1, a /Q = 0). При этом на выходе DD4 напряжение высокого уровня, так как в отсутствие тактовых импульсов (С = 0) на входе А действует напряжение высокого и на входе В - низкого уровня, а с приходом тактового импульса (С = 1) на входе A возникает напряжение низкого, а на входе В - высокого уровня.

Если на вход D подано напряжение низкого уровня, на выходе DD3 будет напряжение высокого уровня, а тактовый импульс, инвертированный элементом DD4, как показано на рис, 5.1,в штрихами, действует подобно сигналу /R. Благодаря этому триггер снова сменит состояние: Q = 0 и /Q = 1.

D-триггер имеет следующую таблицу состояний:

Состояние выхода Q совпадает с состоянием входа D в момент поступления тактового импульса на вход С.

3. Триггер JK- типа. Принцип работы. Временная диаграмма. Функциональная схема. Параметры.  Примеры использования.

Примеры использования.

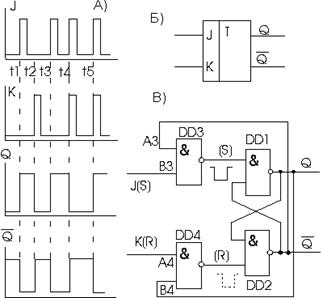

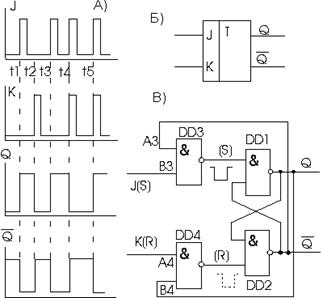

Триггер типа JK представляет собой устройство с двумя устойчивыми выходными состояниями, обладающее двумя информационными входами J и K (рис. 7.1). По принципу действия он сходен с RS-триггером, с той разницей, что в состояниях JK-триггера нет неопределенности при одновременном поступлении сигналов высокого уровня на оба входа. На рис. 7.1В показана схема JK-триггера на ЛЭ И-НЕ. Она отличается от схемы RS-триггера только тем, что элементы DD3 и DD4 включены не как инверторы, а по входам A3 и A4 управляются сигналами с выходов триггера /Q и Q, соответственно.

Работу схемы поясняет рис. 7.1А. Если JK-триггер находится в нулевом состоянии (Q = 0, a /Q = 1 -до момента t1) и на вход J поступит сигнал показанного на рисунке вида, на выходе DD3 за счет связи выхода /Q с входом A3, возникнет сигнал низкого уровня. Он будет действовать подобно

| Рис. 7.1. JK-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с четырмя ЛЭ И-НЕ

| |

сигналу /S на входе /R/S-триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. Если JK-триггер пребывал в единичном состоянии (Q = 1 и /Q = 0 - до момента t2) и сигнал поступит на вход K, то, рассуждая аналогично, можно убедиться, что на выходе DD4 возникает сигнал (показан на рисунке штрихами), который действует подобно сигналу /R, т. е. состояние триггера снова изменится (в этом случае на выходе DD3 напряжение высокого уровня). Когда на обоих входах J и К одновременно напряжение низкого уровня, состояние триггера сохраняется.

Когда на входы J и К одновременно поступает напряжение высокого уровня, дальнейшее поведение триггера зависит от его исходного состояния.

1. Исходное состояние JK-триггера - единичное (Q = 1 и /Q = 0 - после момента t3). За счет связи /Q с A3 на входе A3 = 0 и на выходе DD3 сохраняется напряжение высокого уровня, на которое сигнал J= 1 на входе Вз не влияет. В то же самое время на выходе элемента И-НЕ (DD4) вследствие связи входа В4 с выходом Q (Q = 1) появится сигнал /R, от которого /R/S-триггер, состоящий из DD1 и DD2, сменит состояние (Q = 0, a /Q = l - после момента t4).

| J

| K

| Qn+1

| /Qn+1

|

|

|

| Qn

| /Qn

|

|

|

|

|

|

|

|

|

|

|

|

|

| /Qn

| Qn

|

2. Исходное состояние триггера - нулевое (Q = 0 и /Q = 1 - после момента t4). Рассуждая аналогично, нетрудно убедиться, что на выходе DD4 сохранится напряжение высокого уровня, а на выходе DD3 появится сигнал /S, который сменит состояние /R/S-триггера (Q = 1, /Q = 0 - после момента t5).

Таким образом, в обоих случаях JK-триггер меняет свое состояние. В этом и состоит различие между JK- и RS-триггерами.

Работа JK-триггера определяется следующей таблицей состояний:

Тактируемые триггеры. Особенности. Параметры. Временные диаграммы.

На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим они могут проходить через разное число элементов, не обладающих к тому же одинаковой задержкой. Это явление описывают как состязания или гонки сигналов. В результате в течение некоторого времени на входах создается непредвиденная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию элемента (устройства). Последствия гонок можно устранить временным стробированием, когда на элемент, кроме информационных сигналов, подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают установиться на входах.

Тактируемый триггер, кроме информационных входов, имеет синхронизирующий (тактирующий, тактовый) вход; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на синхронизирующий вход.

На практике наибольшее применение нашли тактируемые D-триггеры. Их назначение обусловлено свойством сохранять предыдущее состояние после снятия входного сигнала до прихода очередного тактового импульса.

На рис. 5.36 изображена принципиальная схема, временные диаграммы работы и условное графическое обозначение синхронного D-триггера, построенного на логических элементах “И-НЕ”. В схеме указаны дополнительные входы  и

и  , называемые входами предустановки, назначение которых – перевод триггера в одно из возможных состояний не дожидаясь прихода тактового импульса.

, называемые входами предустановки, назначение которых – перевод триггера в одно из возможных состояний не дожидаясь прихода тактового импульса.

а) б) в)

Рис. 5.36. Схема D-триггера (а), временные диаграммы работы (б),

условное графическое обозначение (в)

Нижеперечисленные соотношения входных сигналов при наличии на входах  и

и  логических единиц характеризуют принцип работы триггера:

логических единиц характеризуют принцип работы триггера:

С=0, D=0 состояние триггера не меняется; C=0, D=1 состояние триггера не меняется; C=1, D=1 устанавливаются состояния Q=1,  =0; триггер сбросился; C=1, D=0 устанавливаются состояния Q=0,

=0; триггер сбросился; C=1, D=0 устанавливаются состояния Q=0,  =1, триггер установился.

=1, триггер установился.

Триггеры представляют собой импульсные устройства, которые характеризуются наличием двух устойчивых состояний. Простейший триггер имеет два входа и два выхода (рис. 4.1). Выходы обозначают Q и /Q. Выход Q называют прямым, a /Q - инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q = 1, то /Q = 0, либо если Q = 0, то /Q = 1. Необходимо еще отметить, что состояние триггера, при котором Q = 1, a /Q = 0, называют единичным. При нулевом состоянии триггера Q = 0 и /Q = 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется. В зависимости от функциональной связи между логическими сигналами на входах и выходах триггеры в интегральном исполнении имеют следующие наименования: /R/S, RS, D, Т, JK и некоторые другие. Теми же буквами обозначают и входы триггеров.

Триггеры представляют собой импульсные устройства, которые характеризуются наличием двух устойчивых состояний. Простейший триггер имеет два входа и два выхода (рис. 4.1). Выходы обозначают Q и /Q. Выход Q называют прямым, a /Q - инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q = 1, то /Q = 0, либо если Q = 0, то /Q = 1. Необходимо еще отметить, что состояние триггера, при котором Q = 1, a /Q = 0, называют единичным. При нулевом состоянии триггера Q = 0 и /Q = 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется. В зависимости от функциональной связи между логическими сигналами на входах и выходах триггеры в интегральном исполнении имеют следующие наименования: /R/S, RS, D, Т, JK и некоторые другие. Теми же буквами обозначают и входы триггеров. На рис. 4.1 показан простейший триггер - типа /R/S. Здесь использованы только два ЛЭ И-НЕ. Назначение входов: /S-для установки триггера в единичное состояние и /R - для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рис. 4.1, а). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q = 1 и /Q = 0, т. е. триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение высокого, а на выходе - низкого (/Q = 0) уровня. В то же время на одном из входов DD1 напряжение низкого, а на выходе - высокого уровня. Если теперь на вход /S поступает сигнал с обозначенной полярностью (момент t1, рис. 4.1, а), состояние триггера не изменится, потому что поступление сигнала на второй вход DD1 временно изменит только сочетание сигналов на входах (до подачи сигнала оно было 1 и 0, а стало 0 и 0), но выходное состояние DD1 остается при этом неизменным. Если, однако, сигнал поступит на вход /R (момент t2), на обоих входах DD2 уже окажутся напряжения разного уровня, состояние ЛЭ изменится и на выходе его будет напряжение высокого уровня. На обоих входах DD1 окажутся напряжения высокого уровня, а на выходе – низкого, т. е. триггер "опрокинется" и перейдет в другое состояние: Q =О и /Q = 1.

На рис. 4.1 показан простейший триггер - типа /R/S. Здесь использованы только два ЛЭ И-НЕ. Назначение входов: /S-для установки триггера в единичное состояние и /R - для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рис. 4.1, а). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q = 1 и /Q = 0, т. е. триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение высокого, а на выходе - низкого (/Q = 0) уровня. В то же время на одном из входов DD1 напряжение низкого, а на выходе - высокого уровня. Если теперь на вход /S поступает сигнал с обозначенной полярностью (момент t1, рис. 4.1, а), состояние триггера не изменится, потому что поступление сигнала на второй вход DD1 временно изменит только сочетание сигналов на входах (до подачи сигнала оно было 1 и 0, а стало 0 и 0), но выходное состояние DD1 остается при этом неизменным. Если, однако, сигнал поступит на вход /R (момент t2), на обоих входах DD2 уже окажутся напряжения разного уровня, состояние ЛЭ изменится и на выходе его будет напряжение высокого уровня. На обоих входах DD1 окажутся напряжения высокого уровня, а на выходе – низкого, т. е. триггер "опрокинется" и перейдет в другое состояние: Q =О и /Q = 1. Из сказанного следует, что смена состояния триггера происходит только при чередовании сигналов низкого уровня на входах /S и /R. При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q = 0 или Q = 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается.

Из сказанного следует, что смена состояния триггера происходит только при чередовании сигналов низкого уровня на входах /S и /R. При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q = 0 или Q = 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается. Изменение входных сигналов от низкого уровня до высокого приводит к смене состояния триггера (моменты t1, t2, t2 и t5; в момент t4 опрокидывания не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент - t3).

Изменение входных сигналов от низкого уровня до высокого приводит к смене состояния триггера (моменты t1, t2, t2 и t5; в момент t4 опрокидывания не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент - t3). Триггер типа D – это устройство с двумя устойчивыми выходными состояниями. Сменой состояния управляют сигналы на информационном входе D (рис. 5.1), но переключение происходит не сразу, а с приходом тактового импульса на второй вход С. Важнейшее свойство D-триггеров в том, что, как только на вход С поступает импульс, на выходе Q устанавливается тот же уровень напряжения, который в этот момент действует на входе D, т. е. переброс триггера происходит с некоторым отставанием dt относительно смены сигнала на входе D. Поэтому D-триггеры еще называют триггерами задержки.

Триггер типа D – это устройство с двумя устойчивыми выходными состояниями. Сменой состояния управляют сигналы на информационном входе D (рис. 5.1), но переключение происходит не сразу, а с приходом тактового импульса на второй вход С. Важнейшее свойство D-триггеров в том, что, как только на вход С поступает импульс, на выходе Q устанавливается тот же уровень напряжения, который в этот момент действует на входе D, т. е. переброс триггера происходит с некоторым отставанием dt относительно смены сигнала на входе D. Поэтому D-триггеры еще называют триггерами задержки. Примеры использования.

Примеры использования. и

и  , называемые входами предустановки, назначение которых – перевод триггера в одно из возможных состояний не дожидаясь прихода тактового импульса.

, называемые входами предустановки, назначение которых – перевод триггера в одно из возможных состояний не дожидаясь прихода тактового импульса.

и

и  =0; триггер сбросился; C=1, D=0 устанавливаются состояния Q=0,

=0; триггер сбросился; C=1, D=0 устанавливаются состояния Q=0,