Мови програмуванняВідео уроки php mysqlПаскальСіАсемблерJavaMatlabPhpHtmlJavaScriptCSSC#DelphiТурбо Пролог1С Компьютерные сетиСистемное программное обеспечениеИнформационные технологииПрограммирование Linux

Unix

Алгоритмічні мови

Архітектура мікроконтролерів

Введення в розробку розподілених інформаційних систем

Дискретна математика

Інформаційне обслуговування користувачів

Інформація та моделювання в управлінні виробництвом

Комп'ютерна графіка

Лекції

|

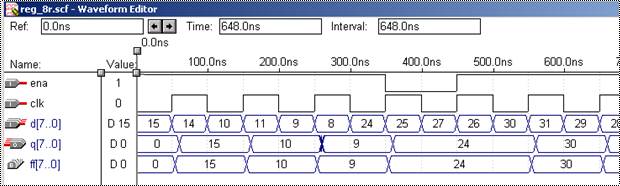

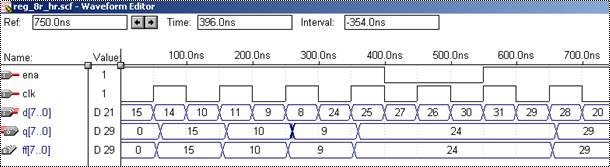

Опис регістрівДата додавання: 2014-11-28; переглядів: 1126.

|

Онлайн система числення Калькулятор онлайн звичайний Науковий калькулятор онлайн

| ||||||||||||||||