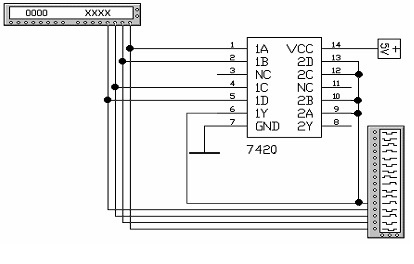

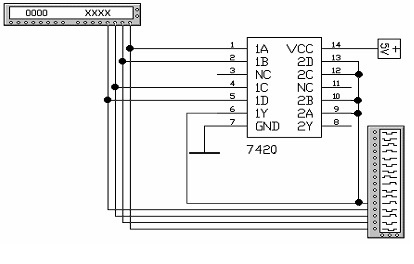

3.3.1 Використовуючи ЛЕ з бункера “Digital ICs” відповідно до заданого варіанта(табл.3.4), зібрати на робочому столі ”Electronics Workbench ”схему, аналогічну рис.3.4. Входи невикористаних ЛЕ ІС приєднати до виходу ЛЕ, що досліджується.

3.3.2 Активізувати ярлик мікросхеми та вибрати логіку “ТТL-LS” для серії 74 та “CMOS-4000 5 V” для серії 4000. Встановіть на генераторі кодів слів такі параметри: Frequency - 9.9 kHz; запуск - External; Pattern - Up Counter. Встановити на логічному аналізаторі такі параметри і режими роботи: Clock mode - Internal; Internal clock rate - 10 kHz.

3.3.3 Одержати на екрані логічного аналізатора часові діаграми сигналів одного із ЛЕ, що входить до складу інтегральної схеми, скласти за нею таблицю істинності і внести її до табл.3.5.

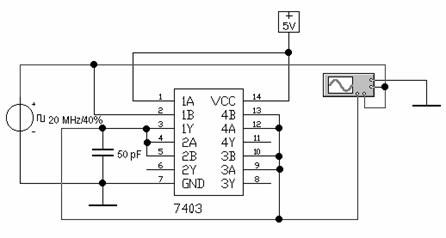

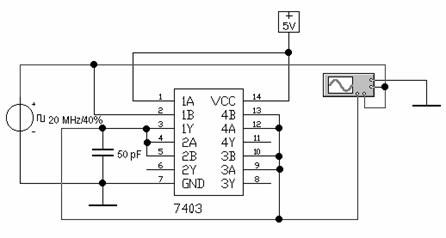

3.3.4 Створіть на робочому столі ”Electronics Workbench ”схему відповідно до рис.3.5. Входи невикористанних ЛЕ ІС приєднати до виходу ЛЕ, що досліджується.

3.3.5 Встановіть такі параметри джерела сигналів: частота - 20 MHz для 74LS та 5 МГц для 4000_5V; коефіцієнт заповнення - 40 %, амплітуда - 5 В.

3.3.6 Виконайте за допомогою осцилографа виміри часу затримки переключення t01 і t10 логічного елемента на рівні

0.5 амплітуди. Результати вимірювань внести до табл.3.5.

Таблиця 3.4 - Таблиця варіантів

| Номер варіанту

| Види ЛЕ

|

|

| 7400_LS і 4072_5V

|

|

| 7408_LS і 4012_5V

|

|

| 7432_LS і 4082_5V

|

|

| 7440_LS і 4025_5V

|

|

| 7420_LS і 4075_5V

|

|

| 7411_LS і 4030_5V

|

|

| 7427_LS і 4000_5V

|

|

| 7451_LS і 4070_5V

|

|

| 7486_LS і 4023_5V

|

|

| 7437_LS і 4077_5V

|

Рисунок 3.4 –Схема з'єднань для одержання таблиці істинності

Рисунок 3.5 - Схема вимірювань динамічних параметрів ЛЕ

Таблиця 3.5 - Результати іспитів і вимірювань

| Назва ЛЕ

| Часові діаграми сигналів

| Часи переключення

|

| (t01), нс

| (t10), нс

| Довід. значення

|

|

|

|

|

|

|

|

|

|

|

|

|