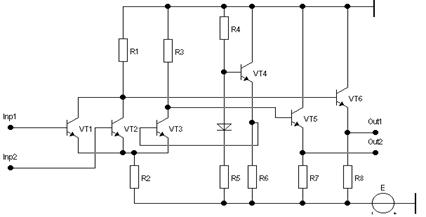

Схема логічного елемента ЕЗЛ - типу показана на рис.3.2

Рисунок 3.2 – Логічний елемент емітерно-зв’язаної логіки

Транзистори VT1, VT2 сприймають вхідні сигнали і разом із транзистором VT3 утворюють диференціальний підсилювач, що працює як перемикач струму, що протікає через резистор R2.

Коли на обох входах є присутнім низький рівень напруги £ -1,6 В, відкритий транзистор VT3, тому що транзистор VT4 і його базове коло створюють на базі транзистора VT3 рівень опорної напруги Uоп = -1,2 В. У результаті цього струм від джерела живлення протікає по колу: резистор R2- транзистор VT3 -резистор R3 і на виході 1 рівень сигналу буде високим, а на виході 2 - низьким.

Якщо на будь-який із входів подати сигнал високого рівня U ≥-0,8 В, відкриється відповідний цьому входові транзистор, що відведе струм через резистор R2 від транзистора VT3 на себе, внаслідок чого транзистор VT3 закриється і на виході 1 рівень стане низьким, а на виході 2 - високим. Таким чином, схема на рис.3.2 виконує функцію АБО по виходу 2 і функцію АБО-НІ по виходу 1 при позитивній логіці (логічна "1" - U ≥-0,8 В; логічний "0" - ≤-1,6 В).

Оскільки транзистори в цій схемі працюють в активній області і не входять у насичення, схема має високу швидкодію. Транзистори VT5, VT6 є емітерними повторювачами і забезпечують великий вихідний струм, а також мають низький вихідний опір, завдяки чому швидкодія елемента мало змінюється при наявності паразитних ємностей на виході.