Реальний режим (Real Mode) відповідає можливостям CPU 8086/8088, дозволяючи адресувати не більше 1 Мбайт пам'яті. З появу процесора 80286 з'явився додатковий сегмент 64кБ верхньої пам'яті. У цьому режимі стартують всі процесори стандарту х86.

Віртуальний режим (Virtual 8086 Mode). Цей режим є особливим станом завдання захищеного режиму, у якому процесор функціонує як 256 незалежних процесорів 8086. На одному процесорі в такому режимі можуть одночасно виконуватися до 256 завдань із ізольованими друг від друга ресурсами.У цьому режимі працює емулятор MS DOS з ОС Windows.

Захищений режим (Protected Mode) з'явився вперше в CPU 80286. У цьому режимі сучасний CPU може адресувати до 4 ГБ фізичної та до 16 ТБ віртуальної пам'яті. Якщо фізична пам'ять повністю завантажена, то дані, що не помістилися у пам'ять, розташовуються на вінчестері у вигляді файлу підкачування. Таким чином, CPU працює не з реальними, а з віртуальними адресами, які управляються за допомогою спеціальних таблиць. Цю пам'ять називають ще віртуальною пам'яттю тому, що фактично вона не існує як єдине ціле.

Захищений режим дозволяє системі запустити кілька захищених друг від друга процесів. Структура цього режиму наведена на мал. 12.3.

Захист пам'яті за допомогою сегментації забороняє:

· використовувати сегменти не за призначенням (наприклад, намагатися трактувати область даних як коди інструкцій);

· порушувати права доступу (намагатися модифікувати сегмент, призначений тільки для читання, звертатися до сегмента, не маючи достатніх привілеїв, та т.п.);

· адресуватися до елементів, що виходять за ліміт сегмента;

· змінювати вміст таблиць дескрипторів (тобто параметрів сегментів), не маючи достатніх привілеїв.

Використовується чотирирівнева ієрархічна система привілеїв, представлена на мал.12.4. Для входу в вищий пріоритет необхідні відповідні права (ліцензія).

0 - Ядро операційної системи та драйвери (вищий ступінь захисту)

1 - Оболонка операційної системи

2 - Менш важливі частини операційної системи

3 – Програма користувача (нижчий пріоритет)

Рис. 12.3. Формування лінійної адреси в захищеному режимі

Рис. 12.4. Рівні привілеїв

В ОС Vista є тільки два рівні привілеїв: ядро операційної системи та програми користувача. Це забезпечує надійність системи та не вимагає перезавантаження системи при установці нових програм.

Контрольні питання

1. З яких основних вузлів складається ядро сучасного процесора?

2. У чому реальність реального режиму?

3. Чому віртуальний режим так називається? У чому його суть?

4. Від чого захищає захищений режим? Як він функціонує?

Лекція 13. Системні технології кешування та Plug & Play

13.1. Кешування інструкцій та даних

У перекладі слово «кеш» (cache) означає склад. Він є додатковим швидкодіючим сховищем копій блоків більшої, але відносно повільної пам'яті, до яких, імовірно, найближчим часом буде звернення.

Кешування - ефективний спосіб підвищення пікової продуктивності системи за рахунок використання буферної пам'яті високої швидкодії.

Рис. 13.1. Послідовність кешування даних

Статична пам'ять ядра процесора кешує ОЗП комп'ютера. ОЗП, у свою чергу, кешує звертання до жорсткого диска, а останній використовується для кешування запису на оптичний диск. Для збереження прийнятної вартості системи використовується кеш-пам'ять невеликого обсягу.

Архітектура кеш. Кеш CPU складається з комірок статичної пам'яті для досягнення максимальної швидкодії, а також контролера пам'яті, що вирішує завдання переміщення даних та інструкцій (Cache=Tag+Data).

Існують наступні архітектури кеш:

· Принстонська, що використовує загальну пам'ять для команд та даних;

· Гарвардська з розділеною областю інструкцій та даних;

· Супергарвардська, що дозволяє обмінюватися даними між областями кеш.

Для багатоядерних процесорів кеш другого L2 та третього L3 рівнів буває роздільним для кожного ядра (Athlon X2), загальним для декількох ядер (Conroe), загальним (L3).

У наш час кеш центрального процесора функціонує з частотою процесорного ядра. При цьому зустрічаються два його типи:

· Інклюзивний (поглинаючий). L1 - 2 такти, L2 - також 2 такти (Pentium).

· Ексклюзивний (доповнюючий) L1 - 2 такти, L2 - 4 такти (Athlon).

Існують також два основних алгоритми запису даних з кеш в основну пам'ять: наскрізний запис WT(Write Through) та зворотний запис WB(Write Back).

Алгоритм WT передбачає виконання кожної операції запису, що попадає в кешований блок, одночасно у рядок кеш та в основну пам'ять. При цьому процесору при кожній операції запису треба очікувати закінчення більш тривалого запису в основну пам'ять. Алгоритм досить простий у реалізації та легко забезпечує цілісність даних за рахунок постійного збігу копій даних у кеш та основній пам'яті. Але ця простота оплачується низькою ефективністю запису. Існують варіанти цього алгоритму із застосуванням відкладеного буферизованого запису, при якому дані в основну пам'ять попадають крізь FIFO-буфер під час вільних тактів шини.

Алгоритм WBдозволяє зменшити кількість операцій запису на шині основної пам'яті. Якщо блок пам'яті, у який необхідно зроблити запис, відображений в кеш, то фізичний запис спочатку буде зроблений в цей дійсний рядок кеш, і рядок буде відзначений як брудний(dirty) або модифікований, тобто потребуючий вивантаження в основну пам'ять. Тільки після цього вивантаження (запису в основну пам'ять) рядок стане чистим (clean), і його можна буде використовувати для кешування інших блоків без втрати цілісності даних. В основну пам'ять дані переносяться тільки цілим рядком (після заповнення всіх його секторів у випадку секторованого кеш) або безпосередньо перед їх заміщенням у кеш новими даними. Даний алгоритм складніше в реалізації, але істотно ефективніше, ніж WT.

Залежно від способу визначення взаємної відповідності рядка кеш та області основної пам'яті розрізняють три способи побудови кеш-пам'яті: кеш прямого відображення (direct-mapped cache), повністю асоціативний кеш (fully associative cache) та їхня комбінація - частково або набірно-асоціативний кеш (set-associative cache).

13.2. Системні ресурси та карта пам'яті в ОС Windows

Сучасний комп'ютер - це взаємодія великої кількості різних цифрових пристроїв. Для їхньої взаємодії необхідно раціональний розподіл ресурсів, які є в системі PC. До системних ресурсів PC відносяться:

· області системної пам'яті - для зберігання даних пристроїв;

· порти введення-виводу (усього 64к) - у тому числі для мережевих пристроїв;

· переривання (як номера, так і функції) - для обслуговування по запиту;

· канали ПДП (15 каналів + UDMA) - для роботи з пам'яттю.

Пам'ять в Windows 95/98 розподіляється на наступні області:

1. Стандартна оперативна пам'ять (Conventional Memory) - перші 640кБ;

2. Апаратна пам'ять (UMA - Upper Memory Area) - 384кБ;

3. Верхня пам'ять (HMA - High Memory Area) - 64кБ. З'явилася внаслідок помилки в процесорі 80286;

4. Розширена пам'ять (XMS - Extended Memory Specification) - розташована вище HMA;

4.1. Розтягнута пам'ять (EMS - Expanded Memory Specification) - перша частина XMS;

5. Віртуальна пам'ять - файл підкачування на HD - продовження пам'яті XMS.

В ОС Windows NT/XP використовується єдиний адресний простір через захищений режим. При цьому в 32-розрядних ОС адреси зовнішніх пристроїв (відеоадаптер, BIOS та ін.) розташовані в 4-му ГБ загального адресного простору. Тому максимальний обсяг ОЗП становить 3,25ГБ. В 64-розрядних системах обсяг ОЗП практично необмежений.

13.3. Технологія Plug & Play

Технологія Plug & Play здійснює автоматизацію підключення пристроїв у систему шляхом розподілу між ними системних ресурсів.

У ПК діють три групи базових апаратно-програмних засобів:

· базова система введення/виводу;

· базова апаратна частина ПК - CPU + контролери на системній платі + слоти розширення PCI (Peripheral Component Interconnect);

· операційна система + додаткове програмне забезпечення.

Взаємодія базових засобів дозволяє автоматизувати процес підключення нових (додаткових) пристроїв до ПК. Процес налаштування здійснюється в такий спосіб:

· установлюються (або вже є в ОС ПК) драйвери нового пристрою;

· за допомогою BIOS або ОС запитується тип пристрою (шина PCI);

· новий пристрій видає ID код;

· відповідно до ID коду виділяються та закріплюються необхідні системні ресурси для нового пристрою.

Контрольні питання

1. Що таке кеш і політика кешування?

2. Наведіть існуючі типи архітектури кеш-пам'яті.

3. Як технологія Plug & Play пов'язана із системними ресурсами?

Лекція 14. Інтерфейси

14.1. Класифікація інтерфейсів

Інтерфейсом називається спосіб з'єднання різних пристроїв системи. На рис.14.1 наведена класифікація різних інтерфейсів.

Найчастіше використовуються такі інтерфейси:

ISA – архітектура індустріального стандарту – шина, розроблена для IBM/PC. У наш час не підтримується в нових розробках.

PCI – Peripheral Component Interconnect – периферійне з'єднання компонентів. Універсальна шина для Pentium-cистем.

PS/2 – порти для підключення миші та клавіатури.

LAN – Local Area Network - мережеве з'єднання.

USB – універсальна послідовна шина.

SCSI – Small Computer System Interface – високошвидкісний інтерфейс для робочих станцій.

IrDA – InterFace Red Data Association.

MIDI – Musical Instrumens Digital Interface – інтерфейс для підключення музичних інструментів.

IDE – Integrated Drivers Electronics - інтерфейс підключення жорстких дисків. Часто використовується еквівалент ATA - AT (поліпшений) attachment або SATA - послідовний ATA. eSATA - для зовнішніх підключень.

Рис. 14.1. Класифікація інтерфейсів

Основні характеристики інтерфейсів зведені в таблицю 14.1.

Таблиця 14.1

| Інтерфейс

| Пропускна

здатність

| Кільк. пристр.

| Гаряча заміна

| Відстань

| Кількість контактів

|

| Послідов. порт COM

| 11кБ/с

|

| Ні

| 10м

| 9(25)

|

| Паралельний порт LPT

| 0.6-2МБ/с

|

| Ні

| 4м

| 25(36)

|

| USB 1.1/2.0 (3.0)

| 0.5..60 (600) МБ/с

|

| Так

| 5м

|

|

| FireWire (IEEE 1394a/b)

| 50/100МБ/с

|

| Так

| 4.5м

|

|

| DialUp 56к

| <6кБ/с

|

| Ні

| >1км

| 2 (RJ-11)

|

| LAN 10/100

| 1…10МБ/с

| 1 (>1)

| Так

| 100м

| 4 (RJ-45)

|

| IrDA

| <500кБ/с

|

| Так

| 3м

| -

|

| BlueTooth

| до 60кБ/с

|

| Так

| 10…100м

| -

|

| 802.11(WiFi)

| >5МБ/с

|

| Так

| 10…100м

| -

|

| ISA

| 1МБ/с

|

| Ні

|

|

|

| PCI / PCI-X

| 0.1-0.5 / 2 ГБ/с

|

| Ні

|

|

|

| PCI Express 16x/1x

| >4ГБ/с

|

| Ні

|

| 164/36

|

| AGP 1x/2x/4x/8x

| 0.26…2ГБ/с

|

| Ні

|

|

|

| Floppy

| 35кБ/с

|

| Ні

| 1м

|

|

| IDE

| 33,66,100,133МБ/с

|

| Ні

| 0.5м

| 40/80

|

| Serial ATA/eSATA(I.II,III)

| 150,300,750MБ/с

|

| Так

| 1м

|

|

| SCSI

| >300MБ/с

|

| Ні

| 6м

| 50…80

|

На практиці FireWire швидше USB на 20%. Хоча теоретична пропускна здатність даної шини на 20% менша, ніж у USB. Дві кручені пари FireWire проти однієї в USB, автономна (апаратна) робота та наявність виділеної шини адреси на практиці приводить до такої ситуації.

14.2. Послідовний інтерфейс (COM)

Послідовний інтерфейс (COM-порт або RS232) спершу призначався для модемного з'єднання. Однак першим пристроєм став маніпулятор «миша». Інтерфейс призначений для повільного (менше 10кБ/с) з'єднання на значну відстань (більше 50м). Діаграми сигналів представлені на рис.14.2, а в таблиці 14.2 наведене призначення контактів послідовного інтерфейсу.

Головний елемент послідовного інтерфейсу - мікросхема 8250 для старих та 16450 UART (Universal Asynchron Receiver Transmitter) для нових плат контролерів. Контролер на базі 8250 забезпечує максимальну швидкість передачі даних 9600 бод, а 16450 - до 115200 бод.

Принцип дії.На відміну від паралельної передачі даних, послідовний зв'язок здійснюється порозрядно. Окремі біти пересилаються (або приймаються) послідовно один за одним, при цьому можливий обмін даними у двох напрямках. Рівень напруги послідовного інтерфейсу змінюється в межах від -12В до +12В.Завдяки цьому відносно високому значенню напруги підвищується завадостійкість, і дані можуть передаватися без втрат по кабелю довжиною 50м та більше. В асинхронному режимі, який використовують ПК (передана команда складається зі стартового біта, 8 біт даних та одного стоп-біта), прийом та передача даних здійснюються з однаковою тактовою частотою.

Рис. 14.2. Діаграми роботи RS232

Таблиця 14.2

| № конт.

| Позначення сигналу

| Вхід/ вихід

| Найменування

|

|

| DCD (Data Carrier Detect)

| Вхід

| Виявлення несучої

|

|

| RXD (Recive Data)

| Вхід

| Прийняті дані

|

|

| TXD (Transmit Data)

| Вихід

| Передані дані

|

|

| DTR (Data Terminal Ready)

| Вихід

| Готовність кінцевого пристрою

|

|

| GND (Ground)

| Корпус

| Сигнальна земля

|

|

| DSR (Data Set Ready)

| Вхід

| Готовність модему

|

|

| RTS (Request To Send)

| Вихід

| Запит передачі

|

|

| CTS (Clear To Send)

| Вхід

| Скидання для передачі

|

|

| RI (Ring Indicator)

| Вхід

| Індикатор дзвінка

|

Швидкість передачі даних. Номінальна швидкість передачі - це швидкість передачі даних, обумовлена кількістю елементів двійкової інформації, переданих за 1с.

Ефективна (реальна) швидкість - це швидкість передачі з урахуванням необхідності передачі службової інформації (що зменшує ефективну швидкість у порівнянні з номінальної) та стискання даних (що збільшує ефективну швидкість).

Швидкість передачі виміряється в бодах, названих на честь французького вченого Жана Моріса Эмиля Бодо. Іноді замість бод уживають позначення bps (bit per second), або біт/с. Однак це трохи різні речі. Величина в бодах вказує кількість переданих біт з урахуванням службових бітів (стартові біти, стоп-биті та біти контролю парності). А величина, зазначена в bps, має на увазі ефективну швидкість передачі самих даних. Типові значення швидкості передачі даних через послідовний інтерфейс для PC та периферійних пристроїв, таких як модеми, становлять 1200, 2400, 4800, 9600, 19200 бод і вище.

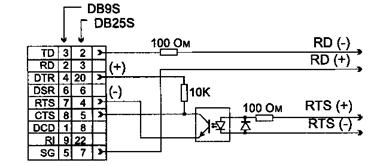

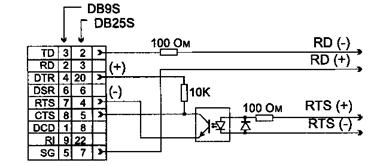

Підключення. Якщо необхідно зв'язати через послідовний інтерфейс два PC, то використовують так званий кабель Null-Modem. Можливі схеми з'єднання двох PC через роз’єм DB9 наведені на рис.14.3 та рис.14.4.

Рис. 14.3. Провідне з'єднання

Рис. 14.4. Оптичне з'єднання

Переривання та адреси. Сом-порти можуть бути сконфігуровані різним образом. BIOS PC підтримує до 4 послідовних інтерфейсів. Стандартні значення адрес та IRQ для Сом-портів наведені в таблиці 14.3.

У наш час COM-порт витісняється інтерфейсом USB.

Таблиця 14.3

| Порт

| Базова адреса

| Лінія переривання

|

| СОМ1

| 3F8h

| IRQ 4

|

| COM2

| 2F8h

| IRQ 3

|

| COM3

| 3E8h

| IRQ 4

|

| COM4

| 2E8h

| IRQ 3

|

14.2. Паралельний інтерфейс (LPT)

Порт паралельного інтерфейсу з’явився в PC для підключення принтера – звідси пішла його назва LPT-порт (Line PrinTer – рядковий принтер). Хоча через цей же порт підключаються також лазерні принтери, які за принципом дії не рядкові, а посторінкові, назва «LPT» закріпилася ґрунтовно.

Адаптер паралельного інтерфейсу являє собою набір регістрів, розташованих у просторі введення/виводу (табл. 14.4). Регістри порту адресуються відносно базової адреси порту, стандартними значеннями якої для порту LPT1 є BASE=378h, для LPT2 – BASE=278h. Порт може використовувати лінію запиту апаратного переривання, зазвичай IRQ7 або IRQ5. Порт має зовнішню 8-розрядну шину даних, 5- розрядну шину сигналів стану та 4- розрядну шину сигналів управління.

Таблиця 14.4

| Ім'я регістра

| Зсув

| R/W

| Опис

|

| SPP Data

| +0

| W

| Регістр даних стандартного порту

|

| SPP Status

| +1

| R

| Регістр стану стандартного порту

|

| SPP Control

| +2

| W

| Регістр керування

|

Призначення:Спочатку використовувався стандарт від фірми Centronics для зв'язку принтера із ПК. Одержав назву SPP (стандартний паралельний порт). Широко застосовується для інших пристроїв: сканери, плотери, а також може використовуватися для підключення адаптера зовнішнього цифрового пристрою. У наш час витісняється інтерфейсом USB.

Розподіл сигналів:Роз’єм містить 25 контактів відповідно до таблиці 14.5. У дужках зазначені альтернативні сигнали в стандарті EPP.

Таблиця 14.5

| № конт.

| Позначення

сигналу

| Вхід/вихід

відн. ПК

| Призначення

|

|

| -STROBE (-WRITE)

| Вихід

| Строб даних (запис)

|

| 2-9

| Data 0 – Data 7

| Вихід/вхід

| Біти даних

|

|

| -ACK# (- INTR#)

| Вхід

| Підтвердження прийому даних (запит на переривання)

|

|

| BUSY# (- WAIT#)

| Вхід

| Принтер зайнятий (очікування)

|

|

| PE (Paper end)

| Вхід

| Кінець паперу

|

|

| SLCT (Select)

| Вхід

| Контроль стану принтера

|

|

| AF (-DATA STB)

| Вихід

| Переклад рядка (строб даних)

|

|

| ERROR

| Вхід

| Помилки

|

|

| -INIT (-RESET)

| Вихід

| Ініціалізація (скидання)

|

|

| SLCT IN (-ADDRSTB)

| Вихід

| Стан On-Line (строб адреси)

|

| 18-25

| GND

|

| Корпус

|